# Renesas RA Family

# Security Design with Arm® TrustZone® - IP Protection

#### Introduction

Arm® TrustZone® technology for ARMv8-M is an optional security extension that is designed to provide a foundation for improved system-level security in a wide range of embedded applications. This application note explains the various RA MCU TrustZone technology enabled hardware and software features and provides guidelines for using these features. In addition, this application project provides step-by-step instructions to kickstart TrustZone technology enabled secure system design with Renesas RA Family MCUs.

For fundamentals of Arm TrustZone Technology, users are encouraged to read the document <u>Arm® TrustZone Technology for the Armv8-M Architecture</u> from Arm. This application project focuses on the TrustZone technology implementation and features for RA Family MCUs with TrustZone support. At the time of release, the RA MCU groups that are covered by this application project includes the MCU groups with support both TrustZone and Device Lifecycle Management, for example, RA6M4, RA6M5, RA4M3, RA4M2, RA6E1, RA4E1 and RA6T2. Support for the MCU groups which do not include Device Lifecycle Management will be added in future release.

Creating a secure design involves using hardware enforcement, software development for security, and tooling support. For TrustZone based security design, tooling plays a critical role for the development, production, and deployment of a product. For the tools support, refer to the <u>FSP User's Manual section:</u> <u>Primer: TrustZone Project Development</u> prior to proceeding to TrustZone based development.

An EK-RA6M4 based application project implementing an IP protection use case for TrustZone technology is provided as a reference project to start application development with the RA Family MCU TrustZone feature. Implementations with e² studio, IAR EWARM and Keil MDK IDEs are provided with instructions on how to import and run the example projects.

#### Required Resources

#### Software and development tools

- e<sup>2</sup> studio IDE v2023-10

- Renesas Flexible Software Package (FSP) v5.0.0

- Renesas Advanced Smart Configurator v2023-10

The links to download the above software are available at <a href="https://github.com/renesas/fsp">https://github.com/renesas/fsp</a>.

- IAR Embedded Workbench for Arm version v9.40.2 or later (<a href="https://www.iar.com/products/architectures/arm/iar-embedded-workbench-for-arm/">https://www.iar.com/products/architectures/arm/iar-embedded-workbench-for-arm/</a>)

- Keil MDK v5.38

(https://www.keil.com/download/product/)

- SEGGER J-Link® USB driver 7.92j or later (<u>SEGGER J-Link</u>)

- Renesas Flash Programmer (RFP) v3.11.01

#### Hardware

- EK-RA6M4, Evaluation Kit for RA6M4 MCU Group (renesas.com/ra/ek-ra6m4)

- Workstation running Windows® 10 and the Tera Term console or similar application

- One USB device cable (type-A male to micro-B male)

# **Prerequisites and Intended Audience**

This application project assumes that you have some experience with the Renesas e² studio IDE, IAR EWARM as well as Keil MDK IDEs. In addition, user is expected be able to understand how to extract the generated content from FSP and Renesas RA Smart Configurator. In addition to reading the two reference documents mentioned in the Introduction section, we recommend reading the first two chapters of the application note *Renesas RA Family Installing and Utilizing the Device Lifecycle Management Keys* to understand the Device Lifecycle States of RA TrustZone technology enabled MCUs. Furthermore, users must know how to enter MCU boot mode using the EK-RA6M4 and create a basic RFP project to communicate with the MCU. This application project only provides necessary settings for the specific functions used in this application project. For more information on the MCU boot mode and RFP, refer to the *Renesas RA6M4 Group User's Manual: Hardware* and *Renesas Flash Programmer User's Manual*.

The intended audience is all users who are or will be developing Arm® TrustZone® based applications using Renesas RA Family MCUs.

#### Contents

| 1.    | Introduction to Arm® TrustZone® and its Security Features | 4  |

|-------|-----------------------------------------------------------|----|

| 1.1   | TrustZone Technology Overview                             | 4  |

| 1.2   | RA MCU Hardware Enforced Security using Arm TrustZone     | 5  |

| 1.2.1 | Memory Separation                                         | 5  |

| 1.2.2 | Bus System Separation                                     | 6  |

| 1.2.3 | IO and Peripheral Separation                              | 7  |

| 1.2.4 | Debug Interface                                           | 8  |

| 1.3   | Device Lifecycle Management                               | 8  |

| 1.4   | Example TrustZone Use Cases                               | 8  |

| 1.4.1 | Intellectual Property (IP) Protection                     | 8  |

| 1.4.2 | Root of Trust Protection                                  | 10 |

| 2     | Arm® TrustZone® Application Design Support                | 10 |

| 2.1   | Renesas Advanced Smart Configurator                       | 10 |

| 2.1.1 | Using RASC with Renesas e² studio                         | 10 |

| 2.1.2 | Using RASC with IAR Embedded Workbench for Arm            | 10 |

| 2.1.3 | Using RASC with Arm Keil MDK                              | 11 |

| 2.2   | Transitioning from CM State to SSD State                  | 11 |

| 2.2.1 | Developing with e <sup>2</sup> studio                     | 11 |

| 2.2.2 | Developing with IAR EWARM                                 | 11 |

| 2.2.3 | Developing with Keil MDK                                  | 11 |

| 2.3   | Setting up the IDAU Region                                | 12 |

| 2.3.1 | Developing with e <sup>2</sup> studio                     | 13 |

| 2.3.2 | Developing with IAR EWARM                                 | 13 |

| 2.3.3 | Developing with Keil MDK                                  | 14 |

| 3.    | General Considerations in TrustZone® Application Design   | 14 |

| 3.1   | Non-secure Callable Modules                               | 14 |

| 3.2   | Guard Function for Non-secure Callables                   | 14 |

| 3.2.1 | Limit Access to Selected Configurations and Controls      | 14 |

| 3.2.2 | Test for Non-secure Buffer Locations                                                     | 15 |

|-------|------------------------------------------------------------------------------------------|----|

| 3.2.3 | Handle Non-secure Data Input Structure as Volatile                                       | 15 |

| 3.2.4 | Limit the Number of Arguments in an NSC Function                                         | 15 |

| 3.3   | Creating User-Defined Non-secure Callable Functions                                      | 16 |

| 3.4   | RTOS Support                                                                             | 16 |

| 3.5   | Writing TrustZone Technology Enabled Software                                            | 16 |

| 3.5.1 | Benefitting from CMSE Functions to Enhance System Level Security                         | 16 |

| 3.5.2 | Avoid Asynchronous Modifications to Currently Processed Data                             | 17 |

| 3.5.3 | Utilize the Armv8-M Stack Pointer Stack Limit Feature                                    | 17 |

| 4. I  | Using Renesas RA Project Generator for TrustZone Development                             | 17 |

| 4.1   | Combined Project Development                                                             | 19 |

| 4.1.1 | Developing the Secure Project                                                            | 19 |

| 4.1.2 | Developing the Non-secure Project                                                        | 25 |

| 4.1.3 | Production Flow Overview                                                                 | 31 |

| 4.2   | Split Project Development                                                                | 31 |

| 4.2.1 | Developing the Secure Bundle and Provisioning the MCU                                    | 31 |

| 4.2.2 | Limitations and Workarounds for Developing in NSECSD State                               | 32 |

| 4.2.3 | Developing the Non-secure Project in NSECSD State                                        | 32 |

| 4.2.4 | Production Flow Overview                                                                 | 34 |

| 4.3   | Flat Project Development                                                                 | 35 |

| 4.3.1 | Operational Flow                                                                         | 35 |

| 4.3.2 | Ethernet Application                                                                     | 35 |

| 4.3.3 | Production Flow Overview                                                                 | 35 |

| 5. I  | Example Project for IP Protection                                                        | 36 |

| 5.1   | Overview                                                                                 | 36 |

| 5.2   | System Architecture                                                                      | 37 |

| 5.2.1 | Software Components                                                                      | 37 |

| 5.2.2 | Operational Flow                                                                         | 38 |

| 5.2.3 | Simulated User's IP Algorithm                                                            | 39 |

| 5.2.4 | User-Defined Non-secure Callable APIs                                                    | 39 |

| 5.3   | Setting up Hardware                                                                      | 40 |

| 5.4   | Example Application with e <sup>2</sup> studio IDE using Split Project Development Model | 42 |

| 5.4.1 | Import, Build, and Program the Secure Binary and Dummy Non-secure Binary                 | 42 |

| 5.4.2 | Import, Build, and Program the Non-secure Project                                        | 45 |

| 5.4.3 | Verify the Example Application                                                           | 47 |

| 5.5   | Example Application with IAR EWARM using Combined Development Model                      | 49 |

| 5.5.1 | Import and Build the Example Projects                                                    | 50 |

| 5.5.2 | Download and Debug the Application Projects                                              | 51 |

| 5.6   | Example Application with Keil MDK using Combined Development Model                       | 54 |

| 5.6.1 | Import and Build the Example Projects                                                    | 54 |

| 5.6.2 Download and Debug the Application Project                  | 58 |

|-------------------------------------------------------------------|----|

| 6. Appendix A: Using Renesas Flash Programmer for Production Flow | 58 |

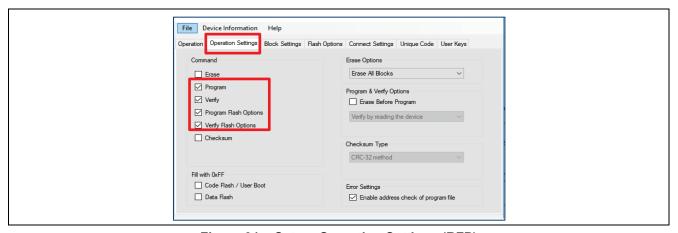

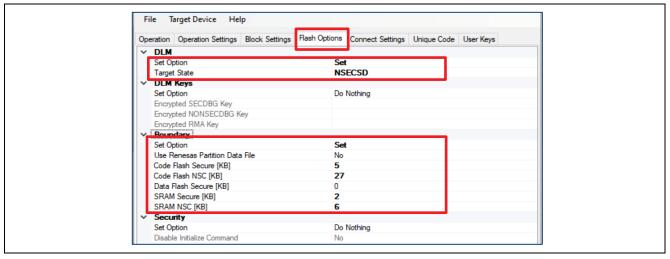

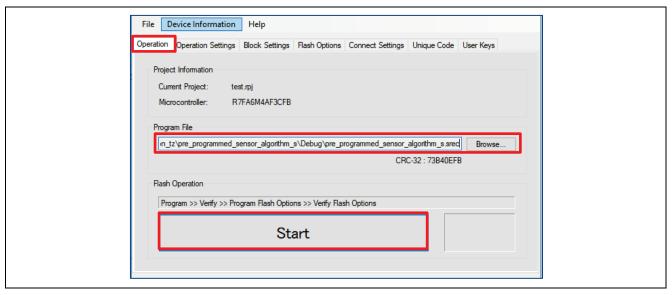

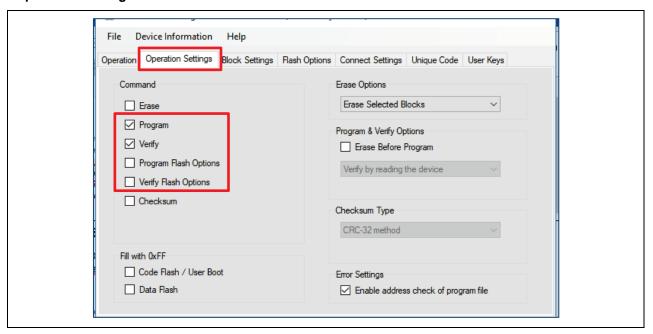

| 6.1 Initialize the MCU                                            | 59 |

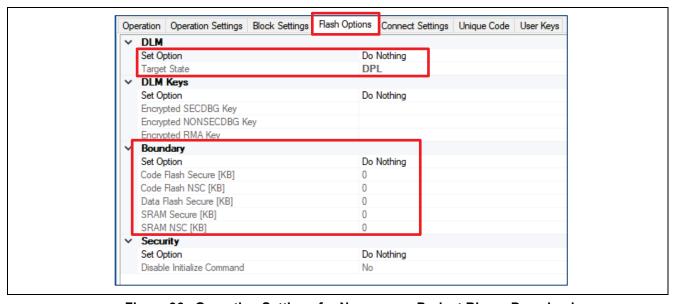

| 6.2 Download the Secure Binary                                    | 59 |

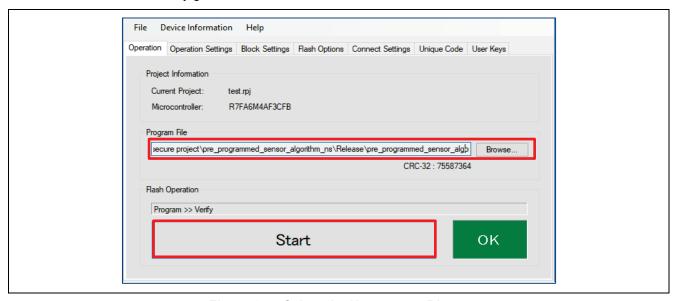

| 6.3 Download the Non-secure Binary                                | 61 |

| 6.4 Specific Instructions to Support IAR EWARM Development Path   | 63 |

| 6.4.1 IAR I-jet and TrustZone Partition Boundary Setup            | 63 |

| 6.4.2 CMSIS-DAP and Trust Zone Partition Boundary Setup           | 63 |

| 7. Appendix B: Glossary                                           | 64 |

| 8. References                                                     | 64 |

| 9. Website and Support                                            | 65 |

| Revision History                                                  | 66 |

# 1. Introduction to Arm® TrustZone® and its Security Features

# 1.1 TrustZone Technology Overview

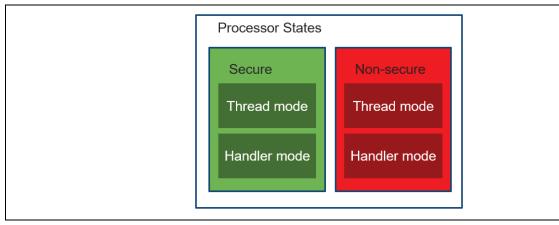

Arm TrustZone technology is a hardware-enforced separation of MCU features. Arm TrustZone technology enables the system and the software to be partitioned into Secure and Non-secure worlds. Secure software can access both Secure and Non-secure memories and resources, while Non-secure software can only access Non-secure memories and resources. These security states are orthogonal to the existing Thread and Handler modes, enabling both a Thread and Handler mode in both Secure and Non-secure states.

Figure 1. Processor States

The Armv8-M architecture with Security Extension is an optional architecture extension. If the Security Extension is implemented, the system starts up in the Secure state by default. If the Security Extension is not implemented, the system is always in the Non-secure state. Arm TrustZone technology does not cover all aspects of security. For example, it does not include cryptography.

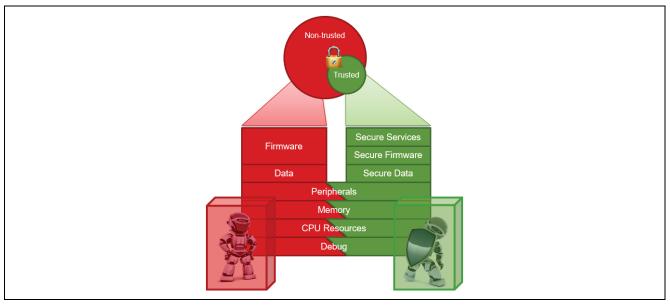

In designs with Armv8-M architecture with Security Extension, components that are critical to the security of the system can be placed in the Secure world. These critical components include:

- A Secure boot loader

- Secret keys

- Flash programming support

- High value assets

The remaining applications are placed in the Non-secure world.

Figure 2. Secure and Non-secure Worlds

As mentioned in the Introduction section, for more details on the definition and usage of TrustZone<sup>®</sup>, see the Arm document, *Arm TrustZone Technology for the Armv8-M Architecture*.

# 1.2 RA MCU Hardware Enforced Security using Arm TrustZone

To build a Secure hardware platform, the security considerations need to go beyond the processor level. Renesas RA Arm TrustZone enabled MCUs extend the security arrangement to the entire system including:

- Memory system

- Bus system

- Access control to Secure and Non-secure peripherals

- Debug system

Note that the RA6M4 MCU Groups are used as a reference in this section. Other TrustZone technology enabled MCUs may have some variations in terms of the details for the hardware features.

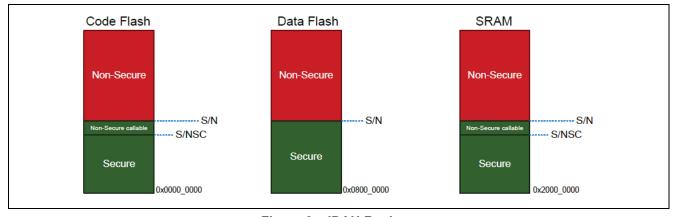

# 1.2.1 Memory Separation

Code flash, data flash, and SRAM on RA TrustZone technology enabled RA MCUs are divided into Secure (S), Non-secure (NS), and Non-secure Callable (NSC) regions by way of the IDAU (Implementation Defined Attribution Unit). These memory security attributes are programmed into the nonvolatile memory using serial programming commands when the device lifecycle is in the Secure Software Development (SSD) state. For the Device Lifecycle State definition and transitions, see the <u>Renesas RA6M4 Group User's Manual:</u>

<u>Hardware</u> section, Security Features.

Figure 3 shows a summary of the 8 available regions.

Figure 3. IDAU Regions

# Code and Data Flash TrustZone® Based Security Features

Code and Data flash regions read from a Non-secure region will generate a TrustZone Secure Fault. Per the MCU design, the Code and Data Flash Programming and Erasing (P/E) mode entry can be configured to be available from only Secure software or from both Secure and Non-secure software.

By default, the MCU configures the Code and Data Flash P/E functionality available only from Secure software. The flash driver may be placed in the Secure partition and may be configured as Non-secure Callable through the FSP to allow the Non-secure application to perform flash P/E operations.

Table 1. Secure Flash Region Read/Write Protection

| Access Violation     | Error Report                                                   |

|----------------------|----------------------------------------------------------------|

| Flash read           | TrustZone Secure Fault: Reset or Non-Maskable Interrupt (NMI). |

| Flash P/E mode entry | Flash P/E Error Flag: Handled by FSP flash driver.             |

RA Family MCUs support temporary and permanent Flash Block Protections for both the Secure region and Non-secure region. For more details on the Code and Data Flash TrustZone technology enabled hardware features, see the *Renesas RA6M4 Group User's Manual: Hardware*, Flash Memory section.

#### **SRAM**

SRAM memory, such as SRAM0, that includes an ECC region and Parity can be divided into Secure/Non-secure Callable/Non-secure regions with Memory Security Attribution (MSA) and can be protected from Non-secure access. When MSA indicates that an SRAM memory region is of Secure or Non-secure Callable status, Non-secure access cannot overwrite them.

Table 2. Secure SRAM Region Read/Write Protection

| Access Violation | Error Report                              |

|------------------|-------------------------------------------|

| SRAM read        | Arm® TrustZone Secure Fault: Reset or NMI |

| SRAM write       | Arm TrustZone Secure Fault: Reset or NMI  |

# 1.2.2 Bus System Separation

The IDAU region setup is consistent for the CPU, Direct Memory Access Controller (DMAC), and Data Transfer Controller (DTC). Master TrustZone filters are implemented for the DMAC and DTC.

#### 1.2.2.1 Master TrustZone Filter for DMA Controller and Data Transfer Controller

The DMAC and DTC are supervised by the Master TrustZone Filter. The TrustZone violation area of Flash and SRAM is detected in advance before accessing the bus. The Master TrustZone Filter in the DMAC or DTC can detect the security areas of Flash area (code Flash and data Flash) and SRAM area (ECC/Parity RAM) defined by IDAU. When a Non-secure channel accesses those addresses, the Master TrustZone Filter detects the security violation. Access to the address in violation is not granted. For both DMAC and DTC, the detected access violation is handled as the "Master TrustZone Filter error". A DMA\_TRANSERR interrupt will be generated in response to the "Master TrustZone Filter error".

Below are some additional comments on the DMAC security attribute:

- The Security Attribution can be configured individually for each channel. Each DMA channel can assume Secure or Non-secure attribute.

- Only Secure code can configure whether the DMAC can be started by Secure or Non-secure code.

- If the DMAC is used in the Secure project, the FSP will start DMA in Secure mode and disable a Non-secure project from accidentally stopping the DMAC by setting up the corresponding registers.

# 1.2.2.2 Ethernet DMA Controller (EDMAC)

The RA6M4 MCU requires EDMAC RAM buffers to be placed in TrustZone Non-secure RAM. The EDMAC is hard-coded as a TrustZone Non-secure bus master. These hardware features allow the following Ethernet code partitioning options:

- Run Ethernet code as Secure and EDMAC RAM buffer in Non-secure RAM.

- Run Ethernet code and EDMAC RAM buffer in Non-secure region.

The FSP supports implementations with both options.

# 1.2.2.3 Bus Master MPU TrustZone® Feature

The Bus Master MPU is available for memory protection function for each bus master except the CPU. Secure software can set up the security attributes of the Bus Master MPU.

Refer to the <u>Renesas RA6M4 User's Manual: Hardware</u> and <u>FSP User's Manual</u> for more details of the security attribute control for the bus systems.

#### 1.2.3 IO and Peripheral Separation

Most peripherals in the MCU can be configured to be Secure or Non-secure with several exceptions as shown in Table 3.

Peripherals are divided into two types:

- Type-1 peripherals have one security attribute. Access to all registers is controlled by one security attribute. Type-1 peripheral security attributes are written to the Peripheral Security Attribution Registers (PSARx: x = B to E) by the Secure application.

- e<sup>2</sup> studio and the FSP provide a convenient way to assign the PSARx.

- Different channels for the peripheral can assume different security attributes. For example, UART Channel 0 and Channel 1 can have different Secure or Non-secure attributes.

- Type-2 peripherals have the security attributes for each register or for each bit. Access to each register

or bit field is controlled according to these security attributes. Type-2 peripheral security attributes are

written to the Security Attribution register in each module by the Secure application. For the Security

Attribution register, see sections in the user manual for each peripheral.

- e<sup>2</sup> studio and the FSP provide configurability for most of these peripherals with several exceptions where sensible default settings have been made to provide a better development experience.

- See the latest <u>FSP User's Manual</u> for details for each peripheral.

Table 3. List of Type-1 and Type-2 Peripherals

| Туре              | Peripheral                                                               |

|-------------------|--------------------------------------------------------------------------|

| Type 1            | SCI, SPI, USBFS, CAN, IIC, SCE9, DOC, SDHI, SSIE, CTSU, CRC, CAC, TSN,   |

|                   | ADC12, DAC12, POEG, AGT, GPT, RTC, IWDT, WDT                             |

| Type 2            | System control (Resets, LVD, Clock Generation Circuit, Low Power Modes,  |

|                   | Battery Backup Function), Flash Cache, SRAM controller, CPU Cache, DMAC, |

|                   | DTC, ICU, MPU, BUS, Security setting, ELC, I/O ports                     |

| Always Non-secure | CS Area Controller, QSPI, OSPI, ETHERC, EDMAC                            |

The access permissions of type-2 peripherals are different by peripheral. See the Register Description section of each peripheral.

Table 4. Peripheral Access Control Based on Arm TrustZone

| Permission                          | Secure access | Non-secure access                                                       |

|-------------------------------------|---------------|-------------------------------------------------------------------------|

| Peripheral configured as Secure     | Allowed       | Write is ignored; read is ignored. TrustZone Access error is generated. |

| Peripheral configured as Non-secure | Allowed       | Allowed                                                                 |

#### **Notes on Clock Generation Circuit (CGC)**

The Clock Generation Circuit has individual security attributes for each of the clock tree controls. The current release of the tooling and FSP provides flexibility of the following clock control schemes:

- Entire clock tree is controlled from the Secure project only and locked down in the Non-secure project.

- Entire clock tree is controllable from the Non-secure project as well as the Secure project.

Refer to *Notes on Clock Control* for the operational details.

# Peripherals that Support Non-secure Partition Operation Only

As shown in Table 3, the following three peripherals have limitations in terms of their security attributes:

- Ethernet: See Section 1.2.2 for the limitations on Ethernet application development.

- CS Area Controller, QSPI, OSPI: These peripherals are Non-secure peripherals only. The FSP has support for them to be used from all three project types. Refer to section 4 for the definitions of project types based on the Project Configurator.

# 1.2.4 Debug Interface

For the Arm® TrustZone® technology enabled RA Family MCUs, the debug function is considered in three levels (DBG0, DBG1, and DBG2) to support TrustZone technology enabled debugging and provide security in development, production, and deployed products:

- DBG2: The debugger connection is allowed and there is no restriction to accessing memories and peripherals.

- DBG1: The debugger connection is allowed and restricted to access only Non-secure memory regions and peripherals.

- DBG0: The debugger connection is not allowed.

Debug level is determined corresponding to the device lifecycle state of product. See the <u>Renesas RA6M4</u> <u>Group User's Manual: Hardware</u> chapter on Security Feature section Device Lifecycle Management for more details.

Debug level regression is possible through the Device Lifecycle Management system. See the application note <u>Renesas RA Family Installing and Utilizing the Device Lifecycle Management Key</u> for the corresponding operational flows.

For Renesas RA TrustZone technology enabled MCUs, J-Link, E2, and E2 Lite debuggers are supported.

# 1.3 Device Lifecycle Management

The RA Family TrustZone technology enabled MCUs incorporate an enhanced Device Lifecycle Management System using TrustZone technology features and Secure Crypto Engine 9 (SCE9). Device Lifecycle Management is important during TrustZone technology enabled application development, production, and deployment stages.

For Device Lifecycle State definition and transitions, see the <u>Renesas RA6M4 Group Hardware User's</u> <u>Manual</u>. For creation, installation, and use of the Device Lifecycle Management keys during development and production stages, see the application note <u>Renesas RA Family Installing and Utilizing the Device</u> <u>Lifecycle Management Keys</u>.

#### 1.4 Example TrustZone Use Cases

This application project explains two specific use cases for TrustZone technology and provides an example software project for the IP Protection use case.

For additional attack scenarios where an attacker may attempt to access protected information and how the TrustZone technology for ARMv8-M can prevent them, see Chapter 2, Security of <u>Arm® TrustZone</u> <u>Technology for the Armv8-M Architecture</u>.

# 1.4.1 Intellectual Property (IP) Protection

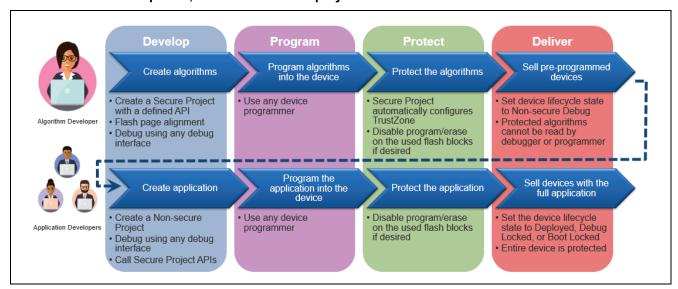

IP protection is a common need for proprietary software algorithms and data protection. TrustZone technology provides good hardware isolation for IP protection. TrustZone technology creates separation between two regions: Secure ("trusted") and Non-secure ("non-trusted") code/data. Users who create building blocks for others to integrate can take advantages of the TrustZone technology feature by storing their software IP in the Secure ("trusted") region.

#### **Business Model**

Not all software developers create end products. Some create building blocks, such as algorithms, for others to integrate into an end product. One difficulty they face is the protection of their software IP. Their end customers would prefer to receive source code, but source code can easily be copied and redistributed. Even binary libraries are not complete protection, as there are tools that can disassemble binaries to assembly and even C source code.

TrustZone® technology enables new business models for these developers in which they can program their algorithms into the secure region of a TrustZone-enabled MCU and sell a value-added MCU, with their IP protected by TrustZone and the Device Lifecycle Management (DLM) system of the RA MCU.

#### **RA MCU Device Lifecycle Management Feature for IP Protection**

During development, DLM state regression allows erasing the protected areas of flash (unless permanently locked). This prevents reading of the protected area of the flash and hence protects the IP and eliminates scrappage of devices in case the algorithms need to be modified.

In production, if the algorithm developer would like to retain the potential to debug algorithms with the application in place, they can install DLM keys for the <u>NSECSD</u> to <u>SSD</u> and <u>DPL</u> to <u>NSECSD</u> transitions. Refer to the <u>Renesas RA Family Installing and Utilizing the Device Lifecycle Management Keys</u> application note for the definition of the device lifecycle states and state regression operational flow.

- SSD: Secure Software Development

- NSECSD: Non-secure Software Development

- DPL: DePLoyed

# **RA MCU Flash Block Locking Feature for IP Protection**

RA MCUs support temporary and permanent Flash Block Protections. This allows customer IP and Root of Trust to be protected from accidental erasure and alteration.

# IP Protection Development, Production and Deployment Flow

Figure 4. IP Protection using Arm® TrustZone®

Designing for IP protection uses the **Split Project Development** model. See section 4.2 for the operational details.

#### 1.4.2 Root of Trust Protection

The Root of Trust (RoT) is a product's security foundation. All higher-level security is built on top of the RoT. The RoT also implements recovery features for higher-level security breaches. When Root of Trust is breached, recovery is not possible and can lead to serious consequences. For IoT applications, Root of Trust may encapsulate authenticated firmware updates and secure internet communication.

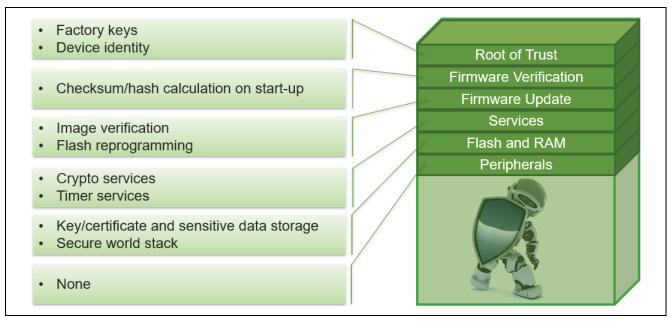

To reduce the attack surface, the functionality included in the RoT should be as little as possible. Typical services in the RoT are described in Figure 5.

Figure 5. Root of Trust Protection - Put as Little as Possible in the Secure Region

All other application code and device drivers should be considered to be allocated to the Non-secure region.

# 2. Arm® TrustZone® Application Design Support

This chapter introduces several IDE features that are established to simplify software development when using the TrustZone hardware isolation with support from other MCU hardware components, FSP software, or tooling.

# 2.1 Renesas Advanced Smart Configurator

The Renesas Advanced Smart Configurator (RASC) implements a project generator which allows TrustZone and Non-TrustZone template projects to be conveniently generated.

# 2.1.1 Using RASC with Renesas e<sup>2</sup> studio

RASC is natively integrated with Renesas e<sup>2</sup> studio IDE.

Section 4 explains how to use the Smart Configurator to start TrustZone development.

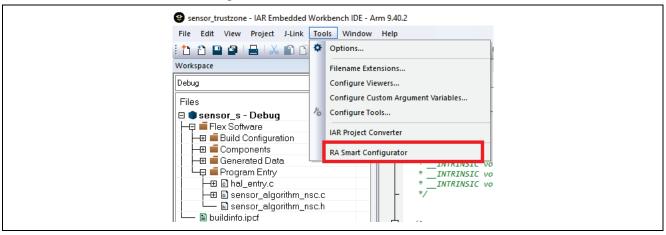

#### 2.1.2 Using RASC with IAR Embedded Workbench for Arm

Create the initial secure project using RASC and choose IAR Compiler. This process will generate the initial secure project for IAR EWARM. Once the initial IAR EWARM project is generated, user can open this project from the IAR EWARM IDE.

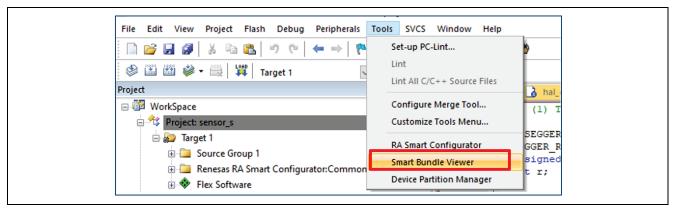

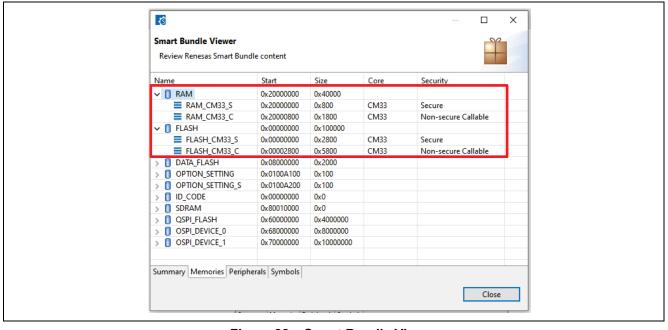

Next, user should follow the <code>rasc\_quick\_start.html</code> file which is installed under <code>\<RASC</code> installation <code>root>\eclipse\</code>. Refer to <code>rasc\_quick\_start.html</code> section Adding tools to a third-party IDE to integrate RASC as well as the Smart Bundle Viewer and the Renesas Device Partition Manager into the IAR EWARM IDE.

Once RASC is integrated in IAR EWARM, you can open RASC within the IAR EWARM IDE to further develop the TrustZone based secure and non-secure project application project following the operations explained in section 4.

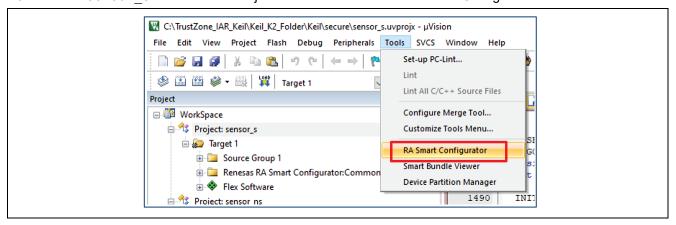

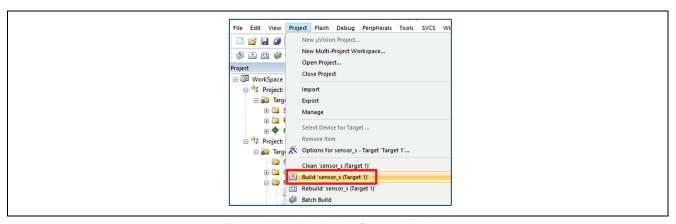

#### 2.1.3 Using RASC with Arm Keil MDK

The operation of using RASC, the Smart Bundle Viewer as well as the Device Partition Manager with Arm Keil MDK to create TrustZone based application is identical to the development process for using RASC with IAR EWARM in terms of the general flow. Note that the Smart Bundle Viewer is needed when using TrustZone with Keil MDK. Section 5.6.2 demonstrated the usage of RASC, the Smart Bundle Viewer as well the Renesas Device Partition Manager (RDPM).

# 2.2 Transitioning from CM State to SSD State

There are some prerequisites prior to setting up the MCU IDAU regions. From the factory, RA MCUs are delivered to the developer in CM (Chip Manufacturing) lifecycle state. The MCU must be transitioned to SSD (Secure Software Development) lifecycle state prior to setting up the IDAU regions.

Transitioning from CM State to SSD State and setting up the IDAU region can only be achieved using the MCU's boot mode, which can only be accessed using an SCI/USB connection. To benefit from the tools support, developers need to bring the MCU Mode pin (MD) and SCI pins to the Debug interface. Special debugger firmware has been developed to manage bringing the device up in SCI boot mode to set up the IDAU registers (automatically drives MD pin) and then switch back to debug mode as needed.

Hardware design must reference the EK-RA6M4 debug interface design (signals in red) to provide proper connections to support the above functionality.

| Pin No. | SWD                            | JTAG                         | Serial Programming using<br>SCI |

|---------|--------------------------------|------------------------------|---------------------------------|

| 1       | VCC                            | VCC                          | VCC                             |

| 2       | P108/SWDIO                     | P108/TMS                     | NC                              |

| 4       | P300/SWCLK<br>Wired OR with MD | P300/TCK<br>Wired OR with MD | P201/MD                         |

| 6       | P109/SWO/TXD9                  | P109/TDO/TXD9                | P109/TXD9                       |

| 8       | P110/RXD9                      | P110/TDI/RXD9                | P110/RXD9                       |

| 9       | GNDdetect                      | GNDdetect                    | GNDdetect                       |

| 10      | nRESET                         | nRESET                       | nRESET                          |

Figure 6. Debug Connection to Support TrustZone® Design

The operational flow when using this feature differs between e<sup>2</sup> studio and the EWARM IDE.

#### 2.2.1 Developing with e<sup>2</sup> studio

When developing with e<sup>2</sup> studio and using Renesas evaluation kits for TrustZone MCUs, the MCU is automatically transitioned from the CM state to the SSD state when the first secure program is downloaded to the MCU if the above required connection is provided.

# 2.2.2 Developing with IAR EWARM

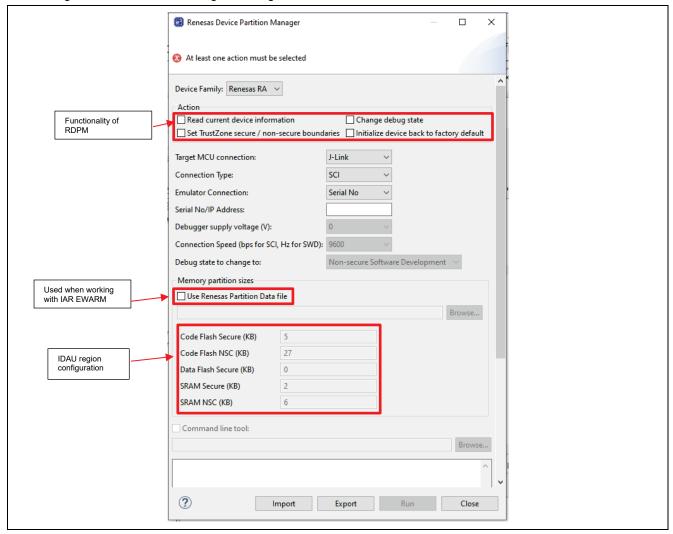

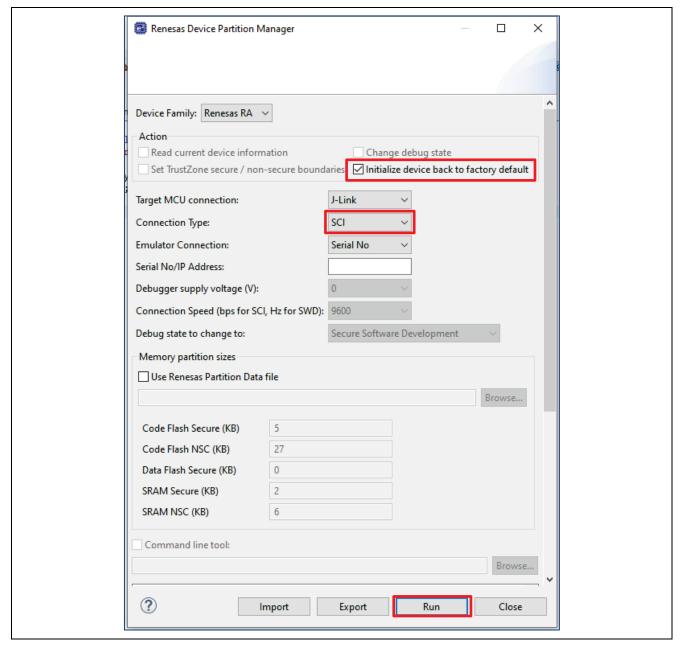

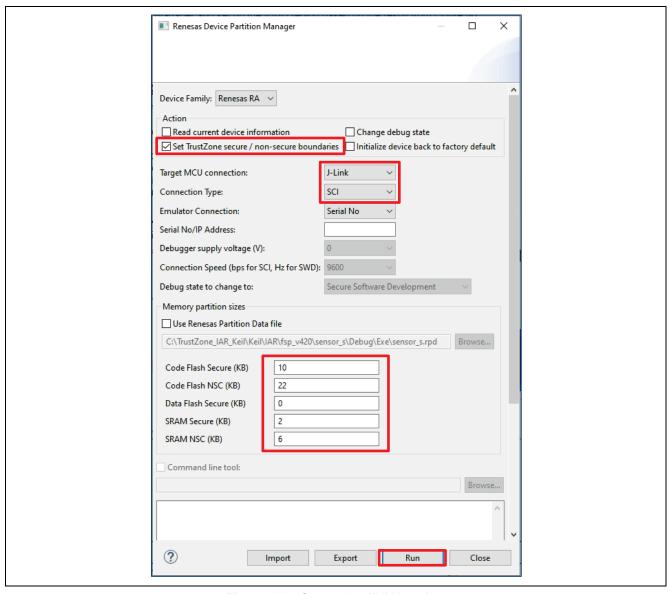

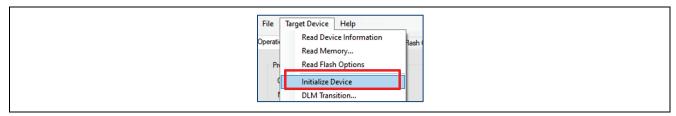

When developing with IAR EWARM, transitioning from CM to SSD needs to be performed manually using Renesas Device Partition Manager or Renesas Flash Programmer. This is achieved by using the **Initialize device back to factory default** option as shown in Figure 7.

#### 2.2.3 Developing with Keil MDK

When developing with Keil MDK, transitioning from CM to SSD needs to be performed manually using Renesas Device Partition Manager or Renesas Flash Programmer. This is achieved by using the **Initialize device back to factory default** option as shown in Figure 7.

# 2.3 Setting up the IDAU Region

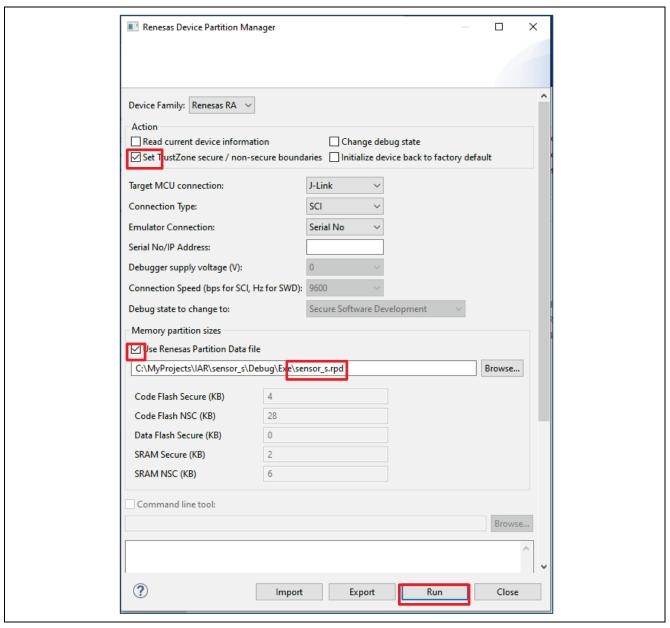

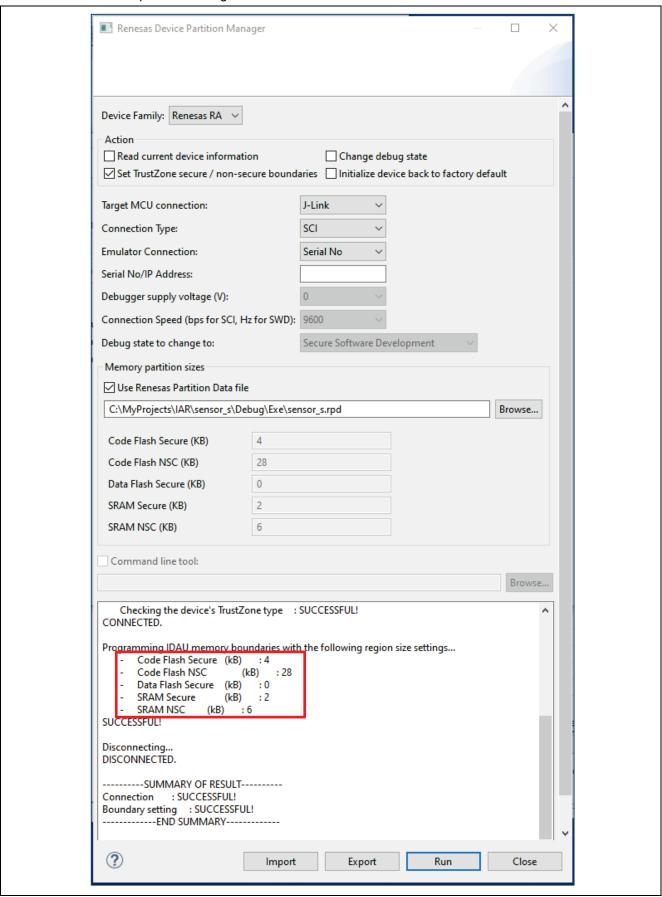

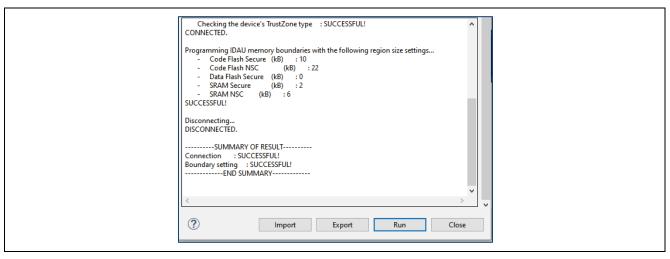

Whether you are using e² studio or a third-party IDE like Keil MDK or IAR EWARM, you can manually set up the IDAU region using RDPM. As shown in Figure 7, the functionalities of the RDPM are under the **Action** area. To set up the IDAU region, select **Set TrustZone® secure / non-secure boundaries** and provide the IDAU region sizes in the IDAU region configuration area.

Figure 7. Functionality of RDPM

The RDPM also provides the following functionalities:

- Use **Read current device information** to read out the DLM and IDAU region setup information.

- Use Change device lifecycle management state to transition to a different state.

- Use Initialize device back to factory default to transition the DLM state to SSD if the device is in NSECSD or DPL state.

When using e<sup>2</sup> studio, the IDAU region configuration is automatically loaded in the dialog box and there are no additional actions needed to fill in the configuration data.

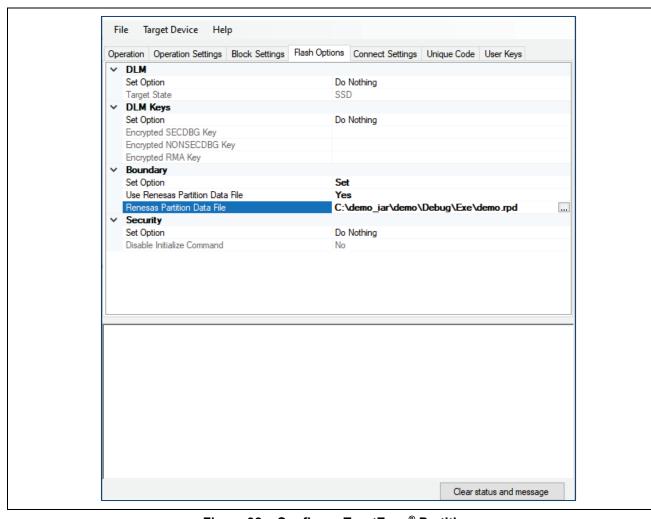

Pay special attention to the check box for **Use Renesas Partition Data file**. This check box is used when setting up the IDAU region using IAR EWARM. You must use the generated <code>.rpd</code> fie to configure the IDAU region. This usage is described in section 5.5. Once an <code>.rpd</code> file is selected, the new IADU region configuration information will be updated automatically based on the <code>.rpd</code> file.

Note: The .rpd filename is stored for future runs. When switching to another project, you must reselect the .rpd file.

The operational flow for using the RDPM differs between e<sup>2</sup> studio, EWARM IDE and Keil MDK, as detailed in the following sections.

# 2.3.1 Developing with e<sup>2</sup> studio

When using e² studio, the necessary values to set up the TrustZone® memory partition (IDAU registers) are calculated after the binary code to program into the Secure region is created by building the Secure project. The regions are set up to ensure that they match the code and data sizes and keep the attack surface as small as possible. If the hardware connection mentioned in Figure 6 is provided in the PCB design, there is no need to use the RDPM manually to set up the IDAU region. Setting up the IDAU region when developing with e² studio is a transparent process for most applications.

#### 2.3.2 Developing with IAR EWARM

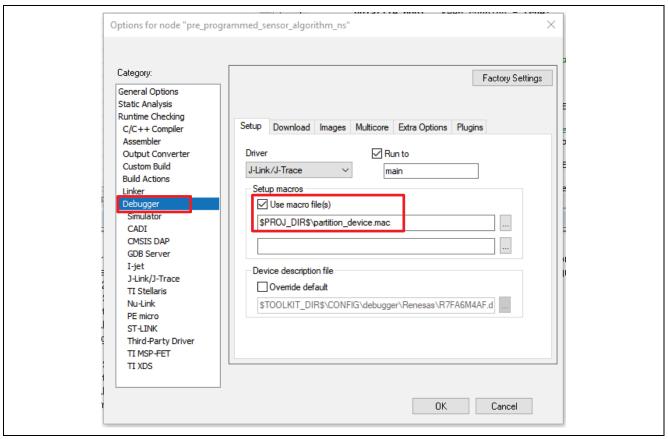

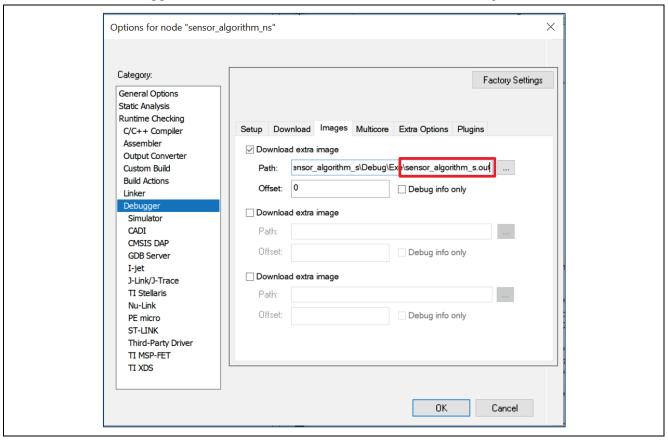

Unlike  $e^2$  studio, setting up the IDAU when developing with IAR EWARM needs to be performed semi-manually using the RDPM. As part of the debug configuration generated when the RASC creates a project for EWARM, there is the invocation of a C-SPY macro file called partition\_device.mac as shown in Figure 8.

Figure 8. Debug Configuration for IDAU Region Setup

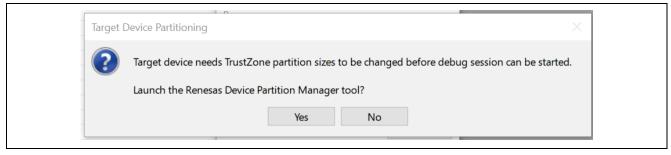

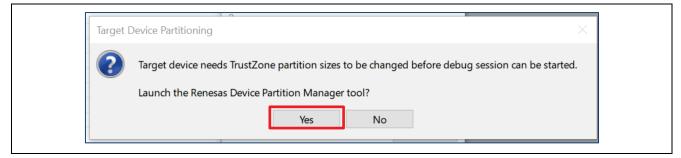

As part of the debug startup sequence, this file will invoke the RDPM integrated to check the target MCU's TrustZone partition boundaries and compare them against the settings calculated as part of the project build sequence. If a mismatch is found, a dialog is displayed asking you whether to reconfigure the IDAU region. You can then choose to launch the RDPM and set up the IDAU regions.

Figure 9. Prompt to Launch the Renesas Device Partition Manager

#### 2.3.3 Developing with Keil MDK

Unlike e<sup>2</sup> studio, setting up the IDAU when developing with Keil MDK needs to be performed manually using the RDPM. The walk through of setting up the IDAU region when working with Keil MDK is demonstrated in section 5.6.1.

# 3. General Considerations in TrustZone® Application Design

# 3.1 Non-secure Callable Modules

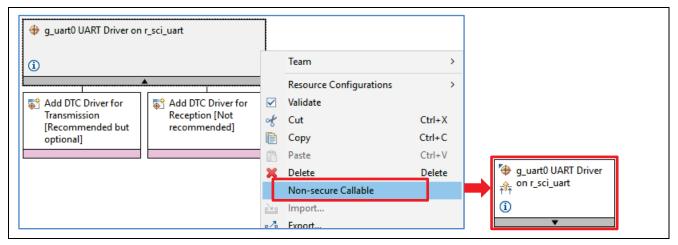

Some driver and middleware stacks in the Secure project may need to be accessed by the Non-secure partition. To enable generation of NSC veneers, set **Non-secure Callable** from the right-click context menu for the selected modules in the Configurator.

Note: It is only possible to configure top of stacks as NSC.

Figure 10. Generate NSC Veneers

#### 3.2 Guard Function for Non-secure Callables

Access to NSC drivers from a Non-secure project is possible through the Guard APIs. The FSP automatically generates guard functions for all the top of stack/driver APIs configured in the Secure project as Non-secure Callable.

Some best practices and guidelines for using the guard functions are listed as follows:

#### 3.2.1 Limit Access to Selected Configurations and Controls

The default guard functions generated ignore  $p\_ctrl$  and  $p\_cfg$  arguments sent in from NS side. Instead, the guard function provides static Secure region instances of these data structures based on the module Instance.

Figure 11. Example Guard Function

#### 3.2.2 Test for Non-secure Buffer Locations

- If the Non-secure region is providing input (such as by calling the write() function with data buffer), then the guard functions should check that data buffer is entirely within an NS area.

- If the Non-secure region is providing a pointer to store output (such as by calling the read() function with a pointer of where to store), then the guard functions should check that the data buffer is entirely within a NS area.

See section 3.5.1 for examples of using the CMSE library to handle this requirement.

# 3.2.3 Handle Non-secure Data Input Structure as Volatile

If a Non-secure region is providing a data structure as input (for example, a typedef'd structure with 3 members), then guard functions should make a copy of the data structure in the Secure region before passing to the Secure function. This is done because Non-secure data structure should be seen as volatile, and the Non-secure region could alter contents after invoking the NSC function.

See section 3.5.2 for an example of how to handle this requirement.

# 3.2.4 Limit the Number of Arguments in an NSC Function

The compiler uses registers R0 to R3 to pass parameters and return values. Registers R4 to R12 are used during function execution. The called function restores registers R4 to R12. Therefore, if an NSC API is being used for a Secure function with more than 4 arguments, the guard function should define a function with a different prototype that will be a funnel to handle all of the arguments. The new function prototype should take a data structure that has members to cover all parameters in the Secure function. This means that Nonsecure code will need to put the function arguments into the structure. The guard function will then expand the data structure into separate arguments and pass them to the Secure function.

Figure 12 shows an FSP example for funneling the 5 arguments from the R\_SPI\_WriteRead function to 4 arguments in the NSC API guard function.

```

/** Non-secure arguments for write-read guard function */

typedef struct st_spi_write_read_guard_args

void const

* p_src;

* p_dest;

void

uint32_t const

length;

spi_bit_width_t const bit_width;

} spi_write_read_guard_args_t;

This function has been modified to reduce the number of arguments. */

BSP_CMSE_NONSECURE_ENTRY fsp_err_t g_spi0_write_read_guard_fanin(spi_ctrl_t *const p_api_ctrl, spi write read guard args t *args)

Verify all pointers are in non-secure memory. */

spi write read guard args t *args checked = cmse check pointed object (args, CMSE AU NONSECURE);

FSP_ASSERT (args == args_checked);

void const *p_src_checked = cmse_check_address_range ((void*) args_checked->p_src, args_checked->length,

CMSE_AU_NONSECURE);

FSP_ASSERT (args_checked->p_src == p_src_checked);

void *p_dest_checked = cmse_check_address_range (args_checked->p_dest, args_checked->length, CMSE_AU_NONSECURE);

FSP_ASSERT (args_checked->p_dest == p_dest_checked);

/* TODO: add your own security checks here */

FSP_PARAMETER_NOT_USED (p_api_ctrl);

return R_SPI_WriteRead (&g_spi0_ctrl, p_src_checked, p_dest_checked, args_checked->length, args_checked->bit_width);

```

Figure 12. Handling Secure Functions with More than 4 Arguments

# 3.3 Creating User-Defined Non-secure Callable Functions

For IP protection purposes, you can create a customized NSC API in the Secure project to expose only the top-level control of your algorithms and store the IP in the Secure Arm® TrustZone® region. Precautions mentioned previously should be exercised during the creation of the user-defined NSC API.

Steps to create a customized NSC API are:

- 1. Create the Non-secure Callable custom function by declaring the function with BSP CMSE NONSECURE ENTRY.

- Create a header file that includes all the customized NSC function prototypes, for example, my nsc api.h.

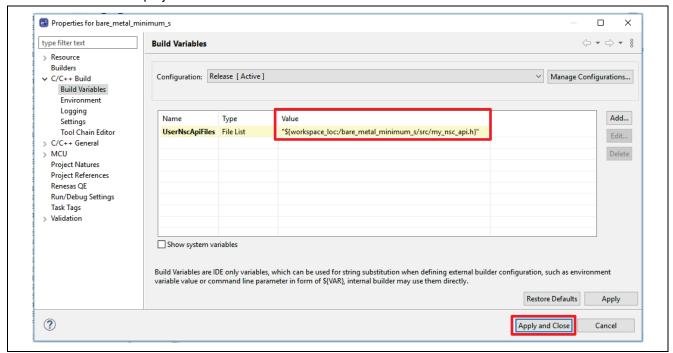

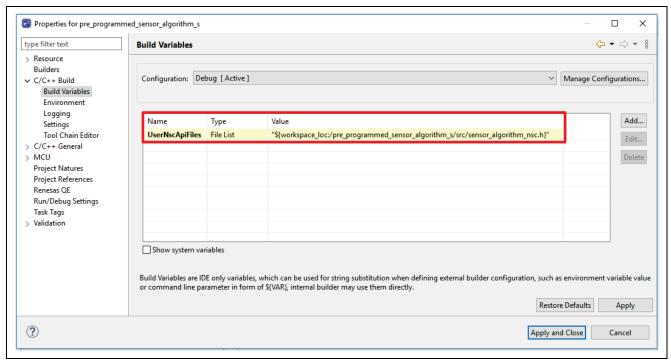

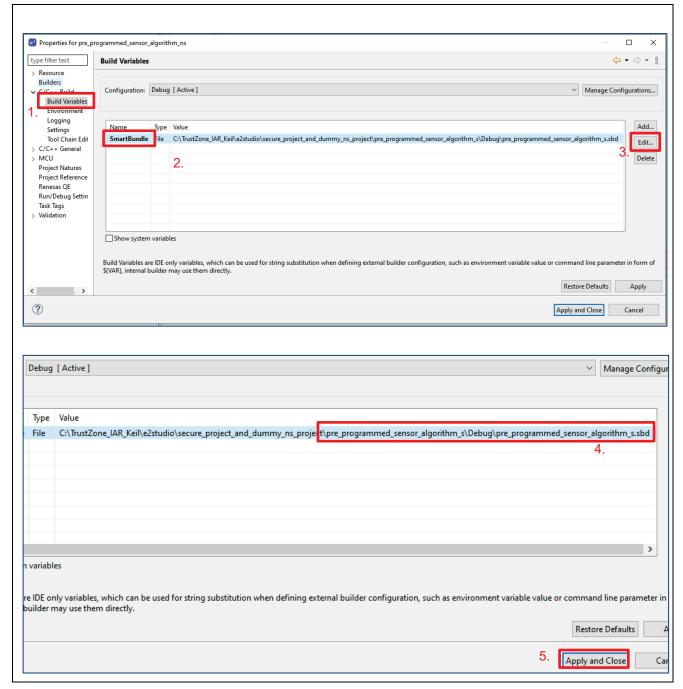

- 3. Include the path to the NSC header using the Build Variable as shown in Figure 13.

- 4. Compile the Secure project to create the Secure bundle. The NSC header will be automatically extracted in the Non-secure project for use.

Figure 13. Link User-Defined Non-secure Callable API Header File

# 3.4 RTOS Support

Renesas tooling and the FSP support Non-secure partition RTOS integration with Secure region access through Non-secure callable APIs. Secure projects can use the **Secure TrustZone Support – Minimum** project type to add the Arm TrustZone Context RA port. For operation details, see section 4.1.1, Step 3 for Secure Project handling and section 4.1.2, Step 5 Non-secure Project Handling.

#### 3.5 Writing TrustZone Technology Enabled Software

Security design using TrustZone technology has some specific challenges that secure developers should bear in mind and take corresponding actions when writing the secure application software.

This section provides several guidelines that secure software developers should consider following in order to avoid Secure information leak to the Non-secure region.

#### 3.5.1 Benefitting from CMSE Functions to Enhance System Level Security

This subsection discusses how to benefit from the CMSE library to improve the secure software design. Some examples of the CMSE functions are:

- cmse\_check\_address\_range: For example, this function can be used to confirm the address range is

entirely in the Non-secure region.

- cmse\_check\_pointed\_object: For example, this function can be used to confirm the memory pointed to by the pointer is entirely in the Non-secure region.

Figure 14. Non-secure Buffer Address Range Check

# 3.5.2 Avoid Asynchronous Modifications to Currently Processed Data

An example of handling is shown in Figure 15. When the pointer p points to Non-secure memory, it is possible for its value to change after the memory accesses used to perform the array bounds check, but before the memory access is used to index the array. Such an asynchronous change to Non-secure memory would render this array bounds check useless.

```

int array[N];

void foo(volatile int *p)

{

int i = *p;

if (i >= 0 && i < N) { array[i] = 0; }

}</pre>

```

Figure 15. Treat Non-secure Data as Volatile in Secure Code

#### 3.5.3 Utilize the Army8-M Stack Pointer Stack Limit Feature

The Armv8-M architecture introduces stack limit registers that trigger an exception on a stack overflow.

CM23 with Arm® TrustZone® technology has two stack limit registers in the Secure state:

- Stack Limit Register for Main Stack: MSPLIM S

- Stack Limit Register for Process Stack: PSPLIM S

CM33 with TrustZone technology has two stack limit registers in the Secure state and two stack limit registers in the Non-secure state:

- Stack Limit Register for Main Stack in Secure state: MSPLIM S

- Stack Limit Register for Process Stack in Secure state: PSPLIM\_S

- Stack Limit Register for Main Stack in Non-secure state: MSPLIM NS

- Stack Limit Register for Process Stack in Non-secure state: PSPLIM NS

Users can implement customized fault handlers to catch the stack limit overflow error.

Refer to <u>Arm®v8-M Architecture Reference Manual</u> section *The Armv8-M Architecture Profile* for more information on the functionality of the stack limit registers.

#### 4. Using Renesas RA Project Generator for TrustZone Development

The RASC is designed for TrustZone technology-based applications. It provides ease of use based on the following implementation features from the tools and FSP point of view:

- RA Project Generator guides you through the TrustZone project creation process.

- TrustZone IDAU region setup during Secure program download, calculated automatically based on the Secure project. See section 2.1 for more details.

- The FSP provides a quick and versatile way to build secure connected IoT devices using Renesas RA MCUs.

Note: FSP version information is removed from the following screen captures because these instructions apply to all FSP versions 5.0.0 or later.

#### **RA Project Generator**

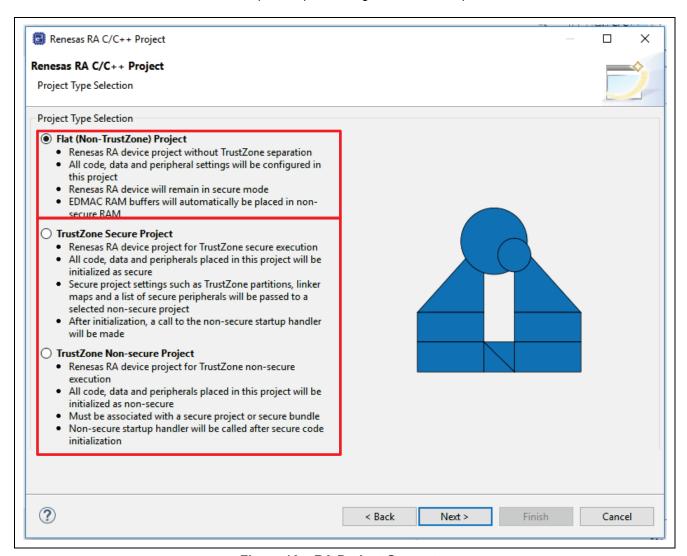

The RA Project Generator provides three project types to create the initial template projects for developing with Arm® TrustZone® technology enabled MCUs:

- A Secure Project and Non-secure Project Type pair which work with the Secure and Non-secure

partitions respectively.

- A Flat Project with which an application can be developed with no TrustZone partition awareness.

- Whether developing with a TrustZone enabled project or with a Flat project, the MCU needs to transit from the CM state to the SSD state prior to proceeding with the development.

Figure 16. RA Project Generator

For RA TrustZone technology enabled MCUs, there are two development models:

- Combined Project Development

- Secure and Non-secure applications are developed by one trusted team.

- Split Project Development

- Secure and Non-secure applications are developed by two different teams.

- The Non-secure application team does not have direct access to Secure partition assets. Access to Secure partition is only possible via Non-secure Callable APIs.

The design process based on each of these two development models are introduced in the subsequent subsections. The design process based on the Flat Project type is introduced in section 4.3.

# 4.1 Combined Project Development

With the Combined Project Development Model, Secure and Non-secure projects are developed by a single trusted team. A Secure project must reside in the same workspace as the Non-secure project and is typically used when a design engineer has access to both the Secure and Non-secure project sources.

In addition, a Secure <code>.elf</code> file is referenced and included in the debug configuration for Debug build for download to the target device. The development engineer has visibility of Secure and Non-secure project source code and configuration.

#### 4.1.1 Developing the Secure Project

Most peripherals and IO defined in the Secure project are configured as Secure with the exceptions of Clock, QSPI, OSPI, and the CS Area. These peripherals can be used in the Secure project and be configured as Non-secure.

The major IDE operational steps in developing the Secure project are explained in the following steps.

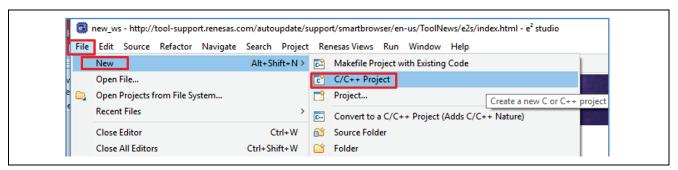

### Step 1: Create a new project using the RA Project Generator template.

Renesas RA MCU tooling provides several project templates to help kickstart development.

Figure 17 to Figure 21 show some common steps when creating a new project with e<sup>2</sup> studio regardless of whether Secure or Non-secure projects are to be created with either the Split Project Development Model or Combined Project Development Model.

- This step will be referenced in the context of Non-secure Project Development for the Combined Project Development Model.

- This step will be referenced in context of Secure and Non-secure Project Development for the Split Project Development Model.

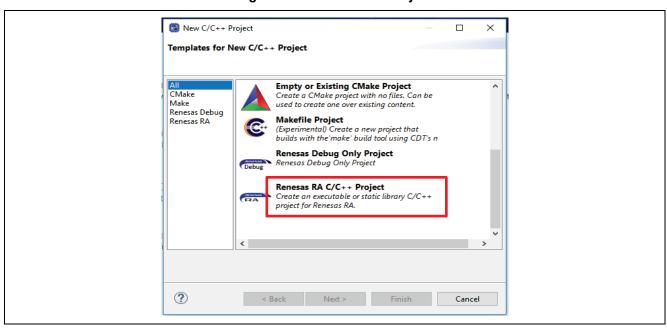

Figure 17. Create New Project

Figure 18. Select "Renesas RA C/C++ Project"

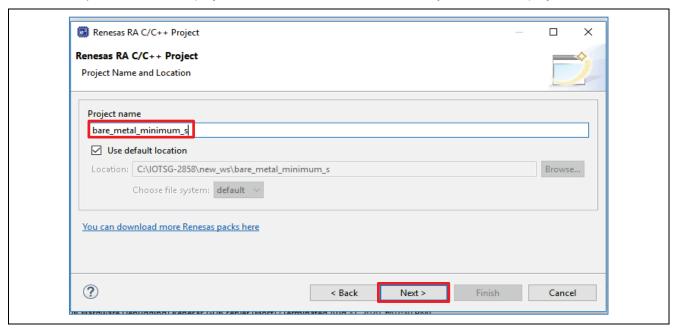

Click **Finish**, then provide the Secure project name. It is helpful to attach "\_s" (for Secure") and "\_ns" (for Non-secure) to the end of the project name as a reminder of the security nature of this project.

Figure 19. Define the Name of the Secure Project

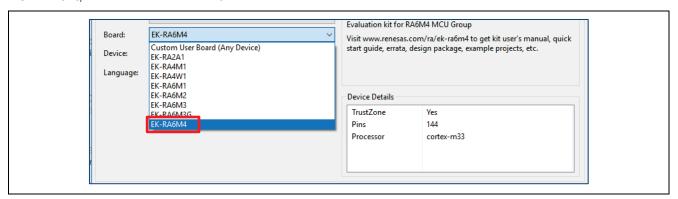

Click Next, then select the EK-RA6M4 BSP.

Figure 20. Select the BSP

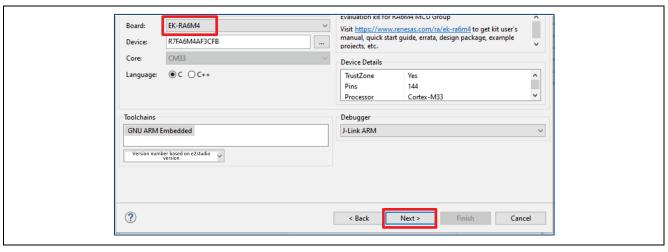

Note: By default, the BSP functionality with regards to security control is only enabled in the Secure project. Once the BSP is selected, click **Next** to view the summary for the hardware setup page.

Figure 21. Review the Configurations Prior to Proceeding to Next Step

Click **Next** and proceed to the following steps.

Note: Step 2 to Step 7 below are common for the Split Project Development Model and Combined Project Development Model. These steps are referred to in context of the Secure Project development for the Split Project Development Model.

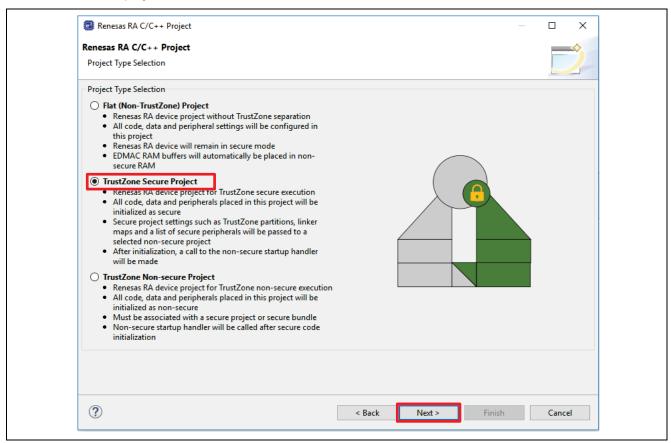

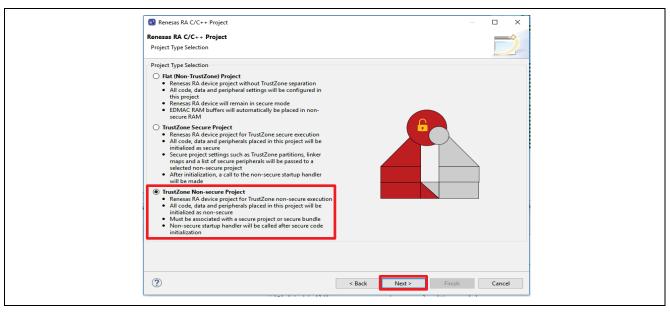

# Step 2: Choose the TrustZone Secure Project as the Project Type.

Choose **TrutZone Secure Project** as the project type and take a moment to read the description on this project type. All peripherals initialized in this project will be assumed to have the Secure attribute with the exceptions indicated in Table 3 as **Always Non-secure**. All code and data placed in this project will be initialized as Secure by the FSP BSP and control will be passed to Non-secure project reset handler at the end of the Secure project execution.

Figure 22. Choose the Secure Project Type

Click **Next** and choose the Project Template.

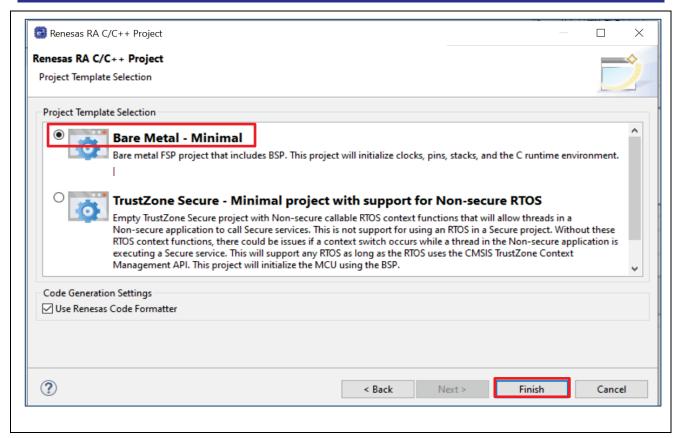

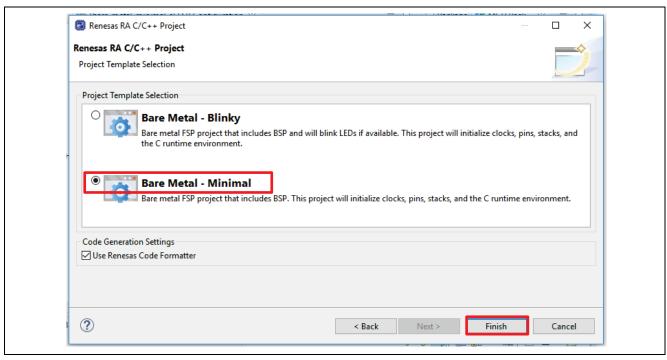

# Step 3: Choose the project template.

As shown in Figure 23, there are two Secure project templates. You can choose which template to use based on whether an RTOS is used in the Non-secure project.

#### • Bare Metal - Minimal

Secure project with MCU Initialization function with support on transitioning to Non-secure partition. This application note uses the **Bare Metal – Minimal** project template as an example to explain the general steps creating a secure project.

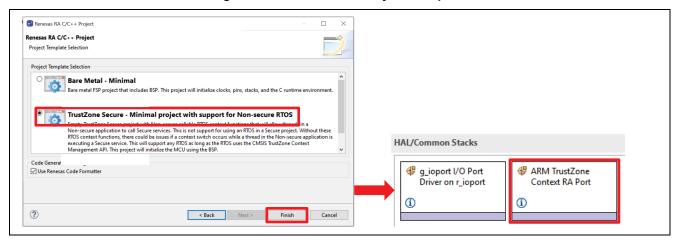

# TrustZone Secure RTOS – Minimal

- Secure projects will add the required RTOS context in the Secure region for the Thread that needs to access the NSC APIs in an RTOS enabled project. When this project type is selected, the Arm TrustZone Context RA Port will be added as shown in Figure 24.

- The RTOS kernel and user tasks will reside in the Non-secure partition.

Figure 23. Choose the Project Template

Figure 24. Adding the TrustZone Context RA Port

Click Finish to allow the Project Generator to populate the project template.

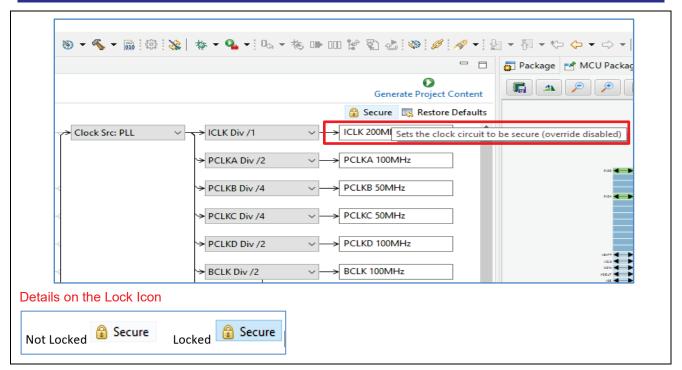

# **Notes on Clock Control**

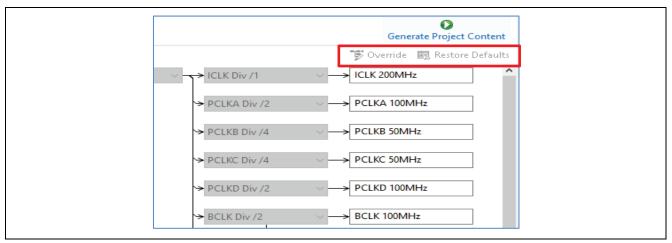

The clock is initialized in the Secure project to allow faster start up. By default, the FSP sets all the security attributes of the Clock Generation Circuit (CGC) to be Non-secure as shown in Figure 25. Therefore, both Secure and Non-secure projects can change the clock setting.

Users have the option to set all the security attributes of CGC as Secure, thus the Non-secure project developer cannot override the secure project setting as shown in Figure 26.

Figure 25. Secure Project Sets Clock as Secure

Figure 26. Non-secure Project Clock control "Override and Restore Default" Disabled Step 4: Generate Project Content and compile the project template.

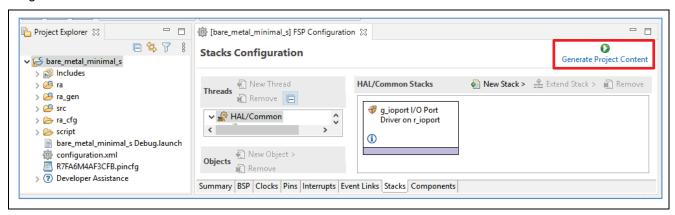

Double click configuration.xml to open the configurator. Click Generate Project Content as shown in Figure 27.

Figure 27. Generate Project Content

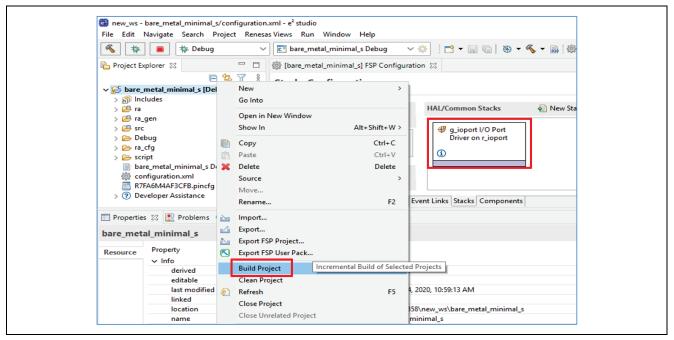

Right-click on the project and select Build Project.

Figure 28. Compile the Template Project

Note: By default, the GPIO driver to control the Secure GPIO pins is included in the template. You can remove the GPIO driver, if is not needed, to reduce the project footprint.

Figure 29 is an example of the compilation result based on Bare-Metal Minimum project template.

```

CDT Build Console [bare_metal_minimum_s]

Building file: ../ra/board/ra6m4_ek/board_leds.c

Building target: bare_metal_minimum_s.elf

arm-none-eabi-objcopy -0 srec "bare_metal_minimum_s.elf" "bare_metal_minimum_s.srec"

arm-none-eabi-size --format=berkeley "bare_metal_minimum_s.elf"

text data bss dec hex filename

```

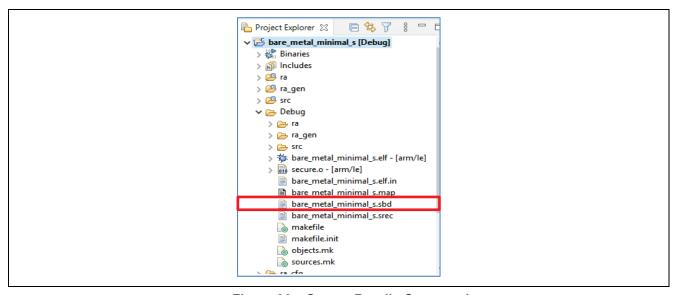

Figure 29. Compilation Result of the Bare-Metal Minimum Secure Template Project Step 5: Review the initial Secure bundle generated.

After successful compilation, the Secure bundle ct\_name. sbd is generated as shown in Figure 30.

Figure 30. Secure Bundle Generated

#### Step 6: Develop the Secure application.

During the product development, it is likely that you will go through the following steps iteratively prior to completing development:

- Add Needed FSP Modules:

- Define NSC Modules if needed. See Section 3.1 for details.

- Note: Ethernet cannot be used in the Secure Project. It is only available in the Non-secure Project.

- Create user-defined Non-secure Callable Functions if needed. See section 3.3 for details.

- Develop the Secure applications:

- Design the code flow such that the Secure applications that are not Non-secure Callable are

executed prior to starting the Non-secure project execution: prior to function call

R BSP NonSecureEnter();

- Recompile and test the application.

#### Step 7: Debug the Secure project in isolation.

With the Combined Project Development Model, the Secure project is typically not debugged in isolation from the Non-secure project. To debug a Secure project on its own, you can use the following options:

- Prepare a "dummy/test" Non-secure project. This approach offers the benefits of allowing the Non-secure Callable APIs to be debugged in the test Non-secure project.

- Replace R\_BSP\_NonSecureEnter(); with while(1); in hal\_entry.c and debug the Secure project by itself. Be sure to restore the R\_BSP\_NonSecureEnter(); after debugging the Secure project prior to provisioning the Secure project to the MCU.

#### Step 8: Debug the Secure project with the Non-secure project.

For the Combined Project Development Model, Secure and Non-secure project development can be debugged in one workspace. Debugging the Secure project typically does not happen in an isolated manner for the Combined Project Development Model. See Section 4.1.2, Step 7 for operational details.

#### 4.1.2 Developing the Non-secure Project

Once the Secure template project is established and compiled, you can start the Non-secure template project creation in the same workspace where the Secure project resides.

# Step 1: Follow Step 1 in section 4.1.1 to start a new Non-secure project.

It is helpful to attach "\_ns" to the end of the project name as a reminder of the security configuration of this project.

#### Step 2: Choose Non-secure project as the Project Type.

Figure 31. Choose Non-secure Project as Project Type

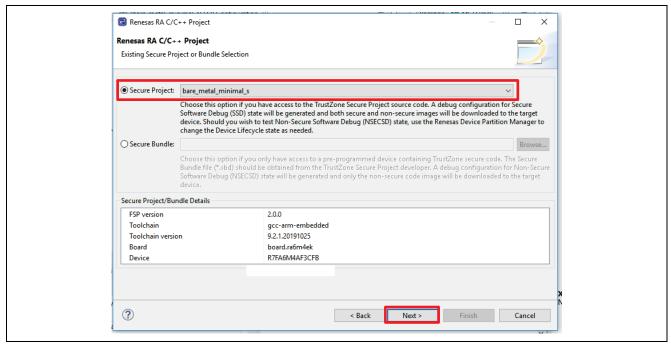

# Step 3: Establish linkage to the Secure project which resides in the same e<sup>2</sup> studio workspace.

Click the down arrow and select the secure project **bare\_metal\_minimum\_s** created in section 4.1.1.

Note: The Secure project must exist in the same workspace AND be open for it to be referenced in the selection box. The Secure project must also be built to create the information used to set up the Non-secure project.

Figure 32. Establish Linkage to the Secure Project

Click Next to proceed.

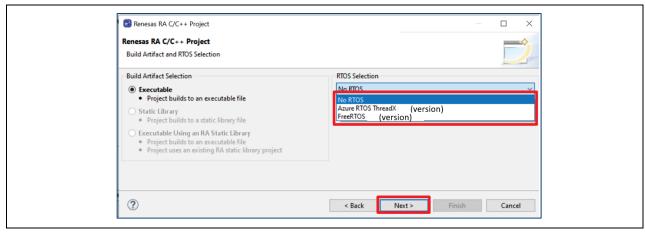

Step 4: Follow the prompt as shown below to choose whether the Non-secure project will have RTOS support.

Figure 33. Choose Whether to Use FreeRTOS in the Non-secure Project

Click Next to proceed.

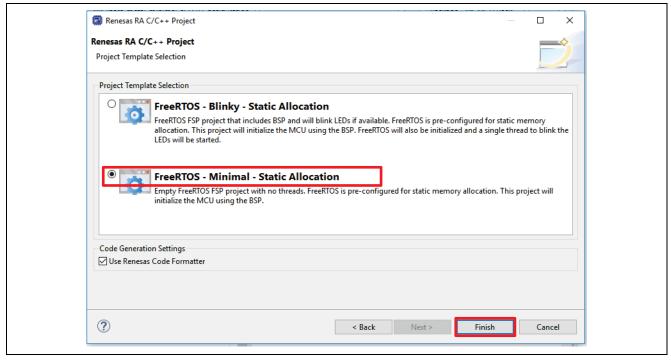

# Step 5: Select the project template to finish creating the Non-secure template project.

If FreeRTOS is selected, the Project Generator provides the following two project templates. Choose the

project template based on the application needs. An example for FreeRTOS is shown as follows. Azure

RTOS has similar options.

Figure 34. Template Options for FreeRTOS Enabled Projects

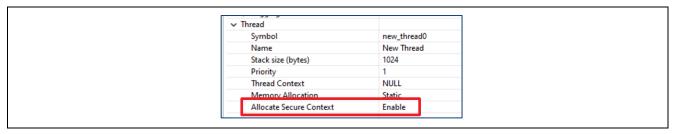

Note: If FreeRTOS is selected and there is access to NSC functions from a Thread in the Non-secure project, it is necessary to enable **Allocate secure context for this thread** in the configurator for that Thread.

Figure 35. Enable Secure Context Allocation

If No RTOS is selected, the Project Generator provides the following two project templates.

Note: The No RTOS selection must be selected if a new RTOS other than FreeRTOS is to be integrated in the Non-secure project.

Figure 36. Template Options for Non-FreeRTOS usage

• Click **Finish** to create the corresponding template project.

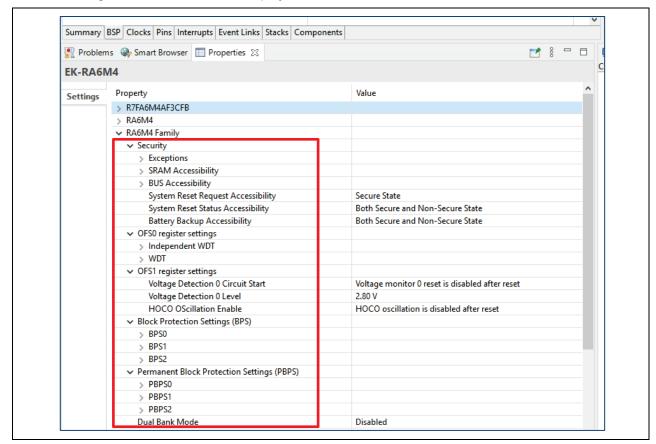

Note: Even though there are security properties allowed for configuration in the BSP **Properties** page, they are not being enabled with the current IDE support. The following attributes cannot be configured from the Non-secure project:

Figure 37. Attributes That Are Not Configurable from a Non-secure Project

By default, the Non-secure project BSP can reconfigure the MCU clock. Refer to Notes on Clock Control.

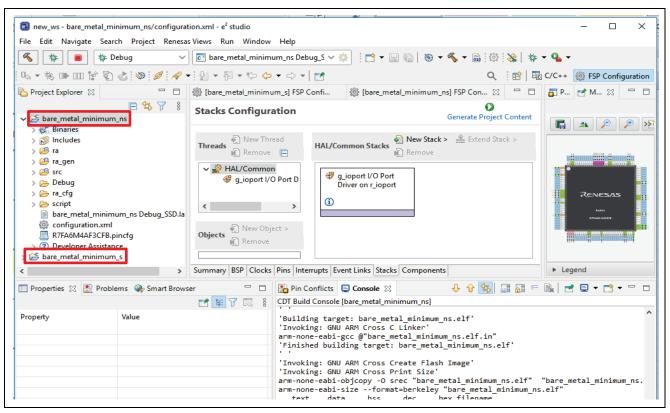

# Step 6: Follow Instructions from Step 1, Section 4.1.1 to Generate Project Content and compile the Non-secure project.

Notice that both the Secure project <code>bare\_metal\_minimun\_s</code> and <code>bare\_metal\_minimum\_ns</code> reside in the same workspace.

Figure 38. Compile the Non-secure Project (No RTOS, Bare-Metal Minimum)

# Step 7: Debug both the Secure and Non-secure projects.

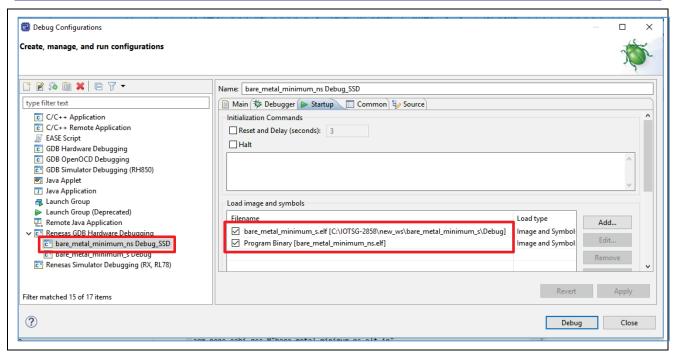

As shown in Figure 39, the debug configuration of the Non-secure project programs both the Secure and Non-secure .elf files to the MCU by default to allow a unified debug session of both the Secure and Non-secure projects.

Notice that cproject\_name> <build\_configuration>\_SSD.launch is generated, as debugging both

Secure and Non-secure projects are performed in device lifecycle state SSD.

Figure 39. Debug Both the Secure and Non-secure Projects

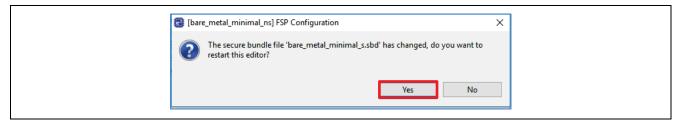

Note: The Secure project must be built each time it is changed to ensure that the connection to the Non-Secure project is maintained. When the Secure bundle changes, there will be a popup window asking you to take the latest Secure bundle. Click **Yes**, then recompile the Non-secure project so that the updated project\_name.sbd will be used.

Figure 40. Secure Bundle Update Notification

# Tips on Ensuring Synchronization between Secure and Non-secure Project

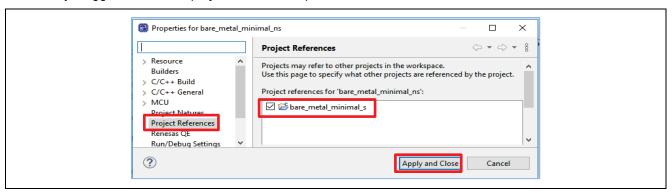

To avoid accidental updates from the Secure Project being missed, you can also define the Secure project as a reference to the Non-secure project so that compiling the Non-secure project will automatically trigger a compilation to the Secure project.

Open the **Properties** page of the Non-secure project, click **Project References** and choose the corresponding Secure project as the Reference project. Once this is set up, compiling the Non-secure project will always trigger the Secure project to be recompiled.

Figure 41. Create Project Reference

#### 4.1.3 Production Flow Overview

This step is for production flow; it is not a step needed during development. Once both Secure and Non-secure project development is finished, you can send the following information to the production line for the MCU to be provisioned prior to selling:

- Secure binary

- Non-secure binary

- IDAU region configuration

Refer to section 6.2 to program the Secure binary and section 6.3 to program the Non-secure binary and transition the MCU state to one of the following device lifecycle states:

- DPL (DePLoyed): The debug interface is disabled temporarily. The serial programming interface is available but cannot access the code and data flash.

- LCK\_DBG (LoCKed DeBuG): The debug interface is permanently disabled. The serial programming interface is available but cannot access the code and data flash.

- LCK\_BOOT (LoCKed BOOT interface): The debug interface and the serial programming interface are permanently disabled.

# 4.2 Split Project Development

Characteristics of the Split Project Development Model include:

- The Secure project and Non-secure project are developed separately by two different teams.

- The Secure project will be developed first by the IP provider. The IP provider creates a Secure bundle.

- The Secure bundle is pre-programmed on the device prior to the Non-secure developer starting their development. Only the Non-secure project and Non-secure partition are visible to the Non-secure developer.

#### 4.2.1 Developing the Secure Bundle and Provisioning the MCU

Developing the Secure project using the Split Project Development Model is very similar to the Combined Project Development Model. However, several key differences are explained in this section.

Step 1: Follow Step 1 to Step 6 from section 4.1.1 to establish the Secure template project and create the applications.

Debugging the Secure project with the Split Project Development Model will not happen with the Non-secure project for the product. As explained in Step 7, section 4.1.1, you can create a dummy Non-secure project for the purpose of Secure project testing, for example to test the Non-secure callable APIs.

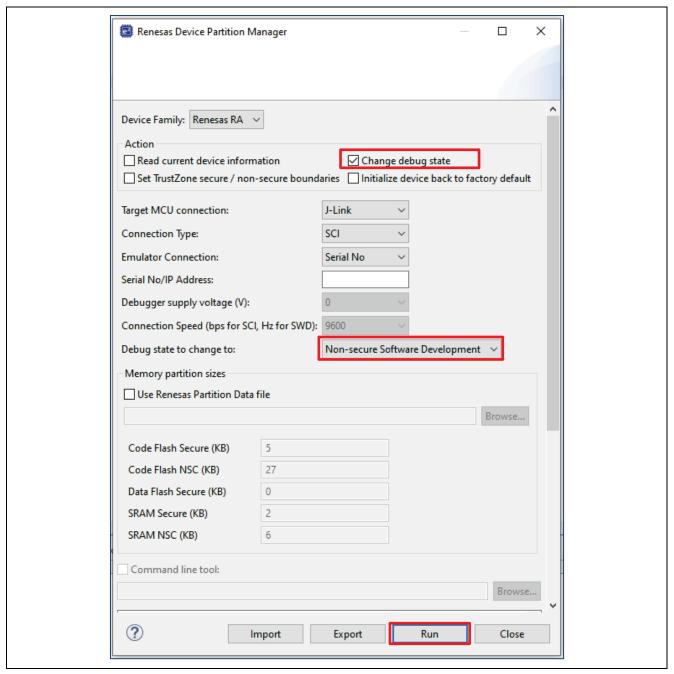

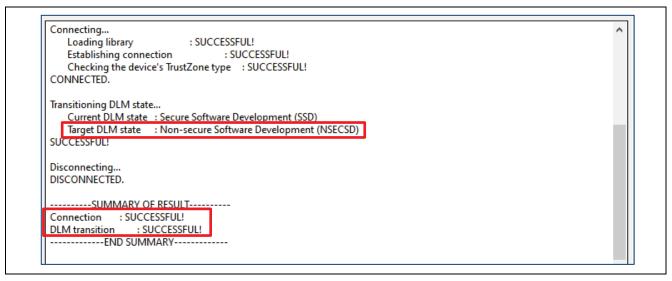

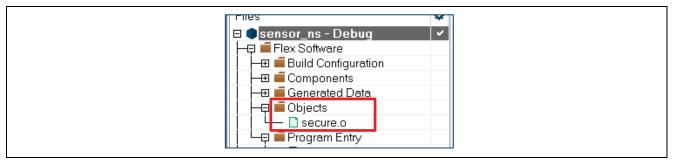

Step 2: Provision the MCU with the Secure project and change the device lifecycle state to NSECSD.

A major difference between Split Project Development and Combined Project Development is that the Secure binary associated with the Secure bundle needs to be provisioned to the MCU prior to the Nonsecure project development for the Split Project Development. The Secure bundle contains the Secure project IP in binary format and the NSC API interface from Secure project. In addition, the MCU device lifecycle state needs to transition from SSD to NSECSD to protect the Secure content.

# 4.2.2 Limitations and Workarounds for Developing in NSECSD State

There is a limitation with the current version of the tools in that a dummy Non-secure project must be provisioned on the device in addition to the Secure binary prior to changing the MCU device lifecycle from SSD to NSECSD with the Split Project Development Model. This is necessary to allow the Non-secure development to resume in the NSEDSD state.

- In the development stage, follow the Combined Project Development Model to prepare a dummy Nonsecure project paired with the intended Secure project. Program the Secure binary and the dummy Nonsecure binary first and then change the device lifecycle state to NSECSD.

- In the production stage, send the following items to the production team:

- Secure binary

- IDAU region setup information

RFP will be used to program the Secure binary and set up the IDAU region. See section 6.2 for the operational details.

- Note that the Secure developer also needs to provide the Secure bundle (cproject\_name>.sbd) to the Non-secure developer to allow Non-secure project to proceed to development.

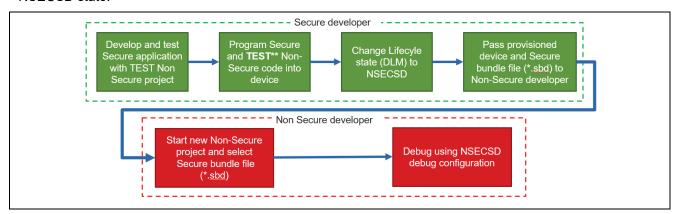

- See Figure 42 for details on the general flow to support Non-secure project development in the NSECSD state.

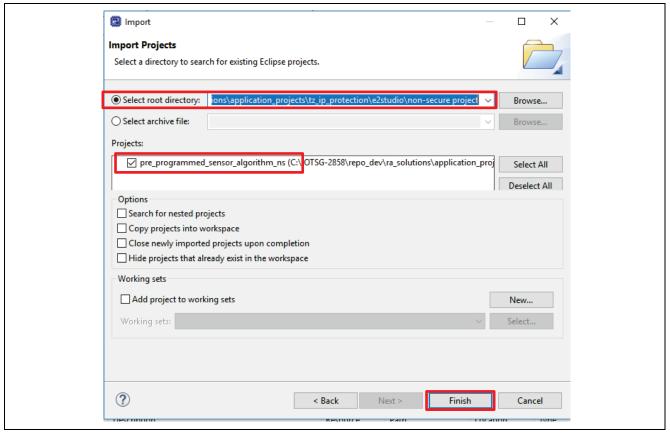

# 4.2.3 Developing the Non-secure Project in NSECSD State

Developing a Non-secure project using the Split Project Development Model has some key differences compared with the Combined Project Development Model.

For the Split Project Development Model, the Non-secure application developer receives the MCU in the NSECSD state. As mentioned towards the end of last section, special handling is needed to enable development in the NSECSD state. Figure 42 is a summary of the general flow for developing in the NSECSD state.

Figure 42. Development Flow for Developing in NSECSD State

Once the Non-secure developers receive the MCU provisioned with the Secure binary, IDAU region, and the Non-secure dummy binary in the NSECSD state, they can use the following steps to proceed to the Non-secure project development:

- Follow step 1 and step 2 in section 4.1.2 to start Non-secure project development.

Typically, the Non-secure project will be created in a different workspace from the Secure project as the Secure project source file and .elf file will not be available for the Non-secure developer.

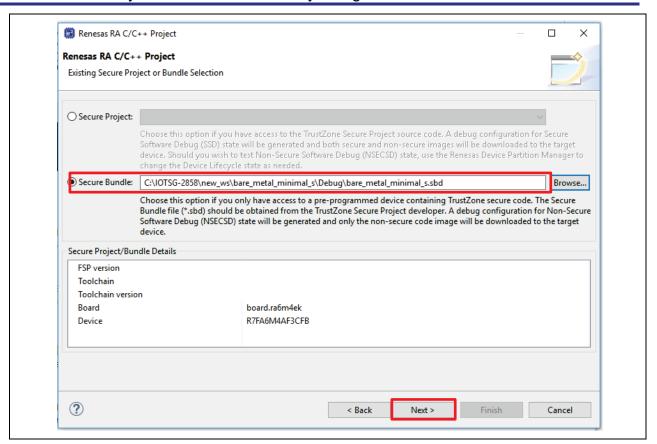

- 2. When the Secure Bundle Selection window opens, choose the secure bundle obtained from the Secure developer.

This step is a key difference between Combined Project Development and Split Project Development process.

The Secure Bundle contains the following information to allow Non-secure project development:

- MCU startup code

- IDAU region setup

- Details of locked Secure peripherals configuration settings

- User-defined Non-secure Callable API interface header file (refer to section 3.3)

Figure 43. Create Linkage to Secure Bundle

Note: The Secure Bundle is linked in with an absolute path. Verify the Secure Bundle linkage whenever the folder location of the project name>.sbd changes.

Follow the prompts to define RTOS usage and select the template project. Once the project is generated, double click configuration.xml to open the smart configurator. Click **Generate Project Content** and compile the project.

Figure 44. Compilation Result of Non RTOS Bare-Metal Minimum Non-secure Project Template

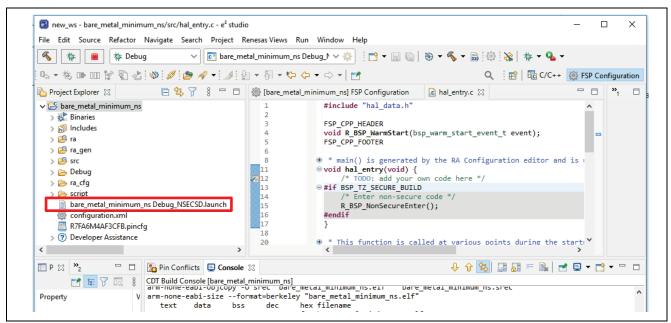

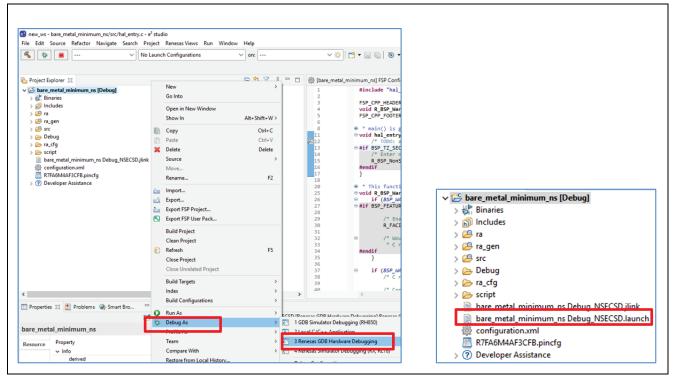

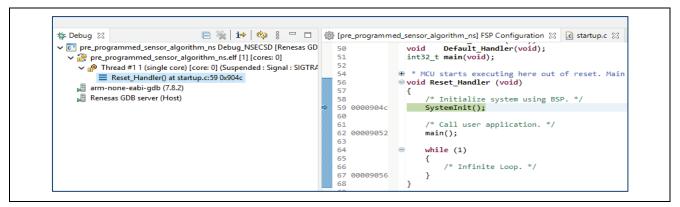

Notice that cproject\_name> <build\_configuration>\_NSECSD.launch is generated as the development is carried out in the NSECSD state.

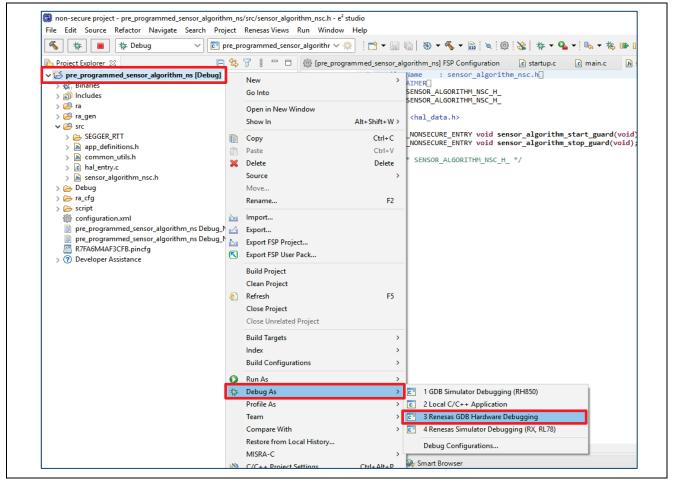

# 4.2.3.1 Debug the Non-secure Project

Prior to debugging the Non-secure project, ensure that the Secure binary as well as the dummy Non-secure binary are programmed on the MCU.

During Non-secure project debugging, only the Non-secure <code>.elf</code> file will be downloaded. There is only the Non-secure project visible in the workspace for the Non-secure developer as opposed to both Secure and Non-secure projects being visible with the Combined Project Development.

Figure 45. Debug the Non-secure Project

#### Notes on updating the Secure Bundle:

- If during Non-secure project development, the Secure Bundle needs to be updated, the Non-secure Developer would need to return the MCU to the Secure Development team for MCU update.

- See section Non-secure Debug in the document FSP User's Manual section: Primer: Arm® TrustZone® Project Development section Non-secure Debug to understand how the tools handle protection of the Secure region when debugging the Non-secure project in the NSECSD Device Lifecycle State.

# 4.2.3.2 Program the Non-secure Project and Transition to DPL Device Lifecycle State

This step is for the production flow. It is not normally needed during Non-secure project development.

Once the Non-secure project is fully debugged, the Non-secure binary can be sent to the production line to program the MCU and transition to the DPL device lifecycle state. Refer to section 6.3 for operational details.

See the application note, *Installing and Utilizing the Device Lifecycle Management Keys* (*R11AN0469*) for information about other possible deployment mechanisms (LCK\_DBG, LCK\_BOOT) as well as the state regression methods utilizing the DLM key through an authenticated procedure.

## 4.2.4 Production Flow Overview

Refer to section 6 to understand the example production flow. For the Split Project Development Model, there can be multiple vendors involved in the production flow:

- Secure image handling vendor: the production team programs the Secure image, sets up the IDAU

boundary, injects the desired DLM and User Keys, and transitions the MCU to the NSECSD state. The

production team also needs to provide the . sbd bundle to the Non-secure application production team.

- Non-secure image handling vendor: the production team programs the Non-secure image and transitions the MCU to a deployment device lifecycle. See section 4.1.3 for the different possible states.

#### 4.3 Flat Project Development

The Flat Project type in the RA Project Generator refers to the development model in which the developer does not need to develop the application with TrustZone® technology awareness:

- One single project handles the entire application.

- Development flow is identical to the Non-TrustZone technology part.

- The MCU operates in the <u>SSD</u> device lifecycle state.

- All peripherals that support Secure and Non-secure attributes will operate in Secure mode.

- Peripherals as identified as Non-secure only in Table 3 will operate in Non-secure mode.

#### 4.3.1 Operational Flow

- 1. Follow Step 1 and Step 2 from section 4.2.1 to start creating the Flat Project template project.

- 2. Select **Flat Project** as the project type from the Project Generator.

- 3. Choose the Build Artifact Selection and RTOS Selection (same interface as in Figure 33).

- 4. The rest of the development is the same as the development for a Non-TrustZone technology enabled MCUs and is out of scope of this application project.

- 5. Debug Flat Project.

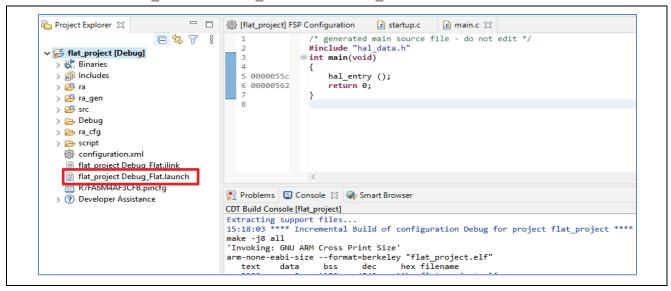

Figure 46. Debug the Flat Project

# 4.3.2 Ethernet Application

In case of using Ethernet with a Flat Project, a 32 KB region is defined as a Non-secure region to support the RAM buffer use of Ethernet. This is automatically handled by the IDE and FSP.

#### 4.3.3 Production Flow Overview

Production of the Flat Project development model will bring in TrustZone technology awareness. The Flat Project development is carried in the MCU lifecycle state SSD. For production deployment, you have the same options as the TrustZone technology aware development model: Split Project Development Model or Combined Project Development Model.

- Option one is to transition the MCU lifecycle state from SSD to NSECSD, then transition to DPL.

- If desired, the MCU lifecycle state can then be transitioned further to LCK\_DBG or LCK\_BOOT.

- Option two is to transition the MCU state from SSD directly to LCK\_DBG or LCK\_BOOT.

Refer to section 4.1.3 for the different possible states.

# 5. Example Project for IP Protection

As discussed in section 1.4.1, IP Protection is a strong use case for TrustZone® technology. The project accompanying this document utilizes the Split Project Development Model to provide an IP protection example TrustZone use case with EK-RA6M4 using the e² studio IDE. The Combined Project Development Model is used for the IAR EWARM and Keil MDK projects.

#### 5.1 Overview

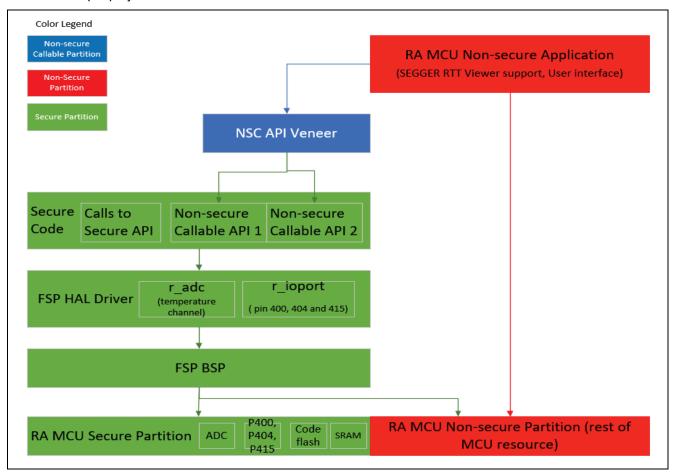

RA6M4 MCUs can be configured to use an ADC peripheral to monitor the on-chip temperature sensor. This application project defines an algorithm to control the LED blinking pattern based on the temperature read from the ADC. The following hardware components are configured as Secure by the Secure project:

- ADC channel for on-chip temperature sensor reading.

- GPIO 400, 404, and 415.

- Secure flash and SRAM setup by the IDAU.

The following software components are configured as Secure by the Secure project:

- The FSP ADC HAL driver.

- The FSP GPIO HAL driver for the corresponding LED driving pins.

- The application code that starts, scans, and stops the ADC.

- The application code that controls the LED blinking pattern based on the temperature reading.

- The API that starts the monitoring and reacting algorithm.

- This API is defined as Non-secure Callable API and its veneer is exposed to the Non-secure partition.

- The API that stops the monitoring and reacting algorithm.

- This API is defined as Non-secure Callable API and its veneer is exposed to the Non-secure partition.

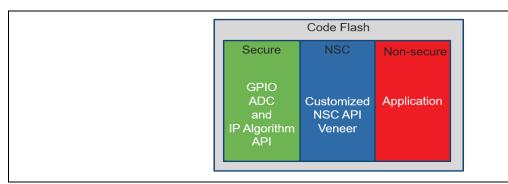

Figure 47. Sensor Algorithm IP Protection

## 5.2 System Architecture

#### 5.2.1 Software Components

Figure 48 shows the Secure, Non-secure, and Non-secure Callable hardware and software partition scheme in this example project.

Figure 48. Software Architecture Block Diagram

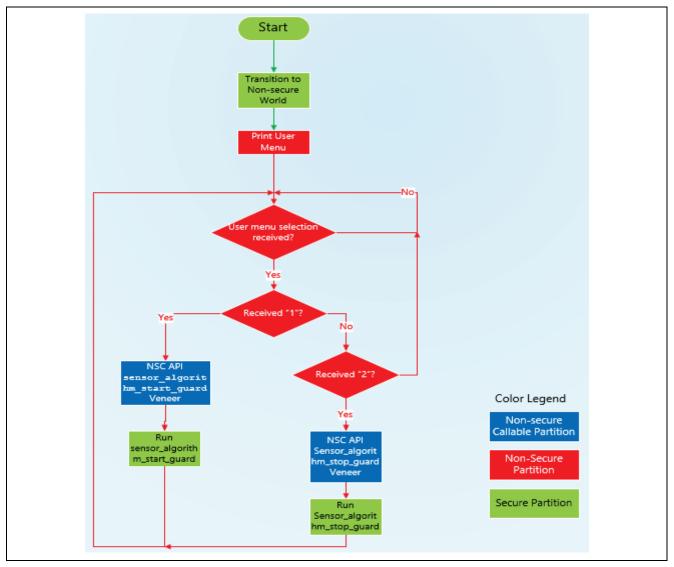

#### 5.2.2 Operational Flow

Figure 49 shows the system-level operational flow of the example project.

Figure 49. Operational Flow

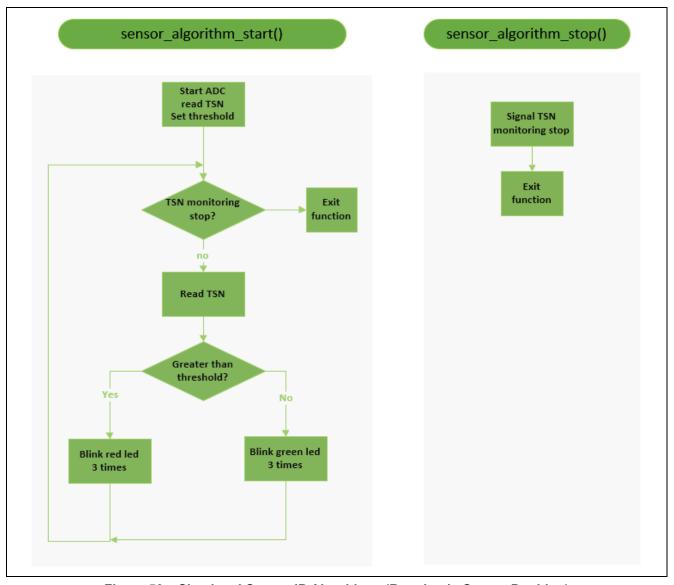

## 5.2.3 Simulated User's IP Algorithm

The simulated user's IP algorithm is described in Figure 50.

Note: In Figure 50, TSN means on-chip Temperature Sensor.

Figure 50. Simulated Sensor IP Algorithms (Running in Secure Partition)

#### 5.2.4 User-Defined Non-secure Callable APIs

The Non-secure callable functions exposed to the Non-secure partition are defined in  $sensor\_algorithm\_nsc.h$  from the Secure project.

```

# File Name : sensor_algorithm_nsc.h

* * DISCLAIMER

* #ifndef SENSOR_ALGORITHM_NSC_H

#define SENSOR_ALGORITHM_NSC_H

#include <hal_data.h>

BSP_CMSE_NONSECURE_ENTRY void sensor_algorithm_start_guard(void);

BSP_CMSE_NONSECURE_ENTRY void sensor_algorithm_stop_guard(void);

#endif /* SENSOR_ALGORITHM_NSC_H_ */

```

Figure 51. User-Defined NSC APIs

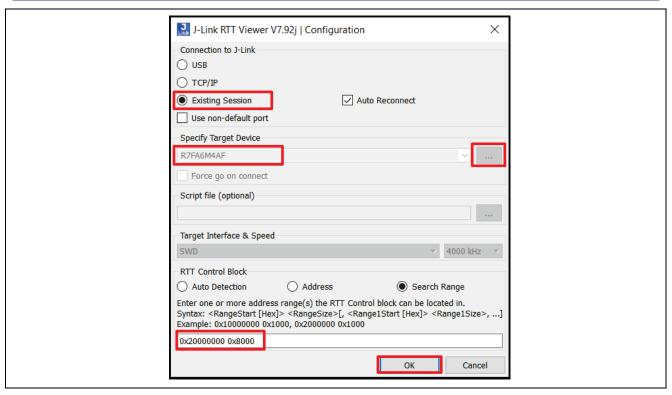

To share the user-defined NSC calls, this header file is linked to e<sup>2</sup> studio by a Build Variable.

The path to this header file is added using the Build Variable UserNscApiFiles as shown in Figure 52.

Figure 52. User Build Variable to Link User NSC Header File (Secure Project Setting) in e<sup>2</sup> studio

The Build Variable approach does not exist when using IAR EWARM and Keil MDK; you need to manually share this header file with the Non-secure project. This is demonstrated in the included IAR EWARM and Keil MDK example project.

## 5.3 Setting up Hardware

- Jumper setting default EK-RA6M4 setting.

- See <u>EK-RA6M4 User's Manual</u>.

- Connect J10 using USB macro to B cable from EK-RA6M4 to the development PC to provide power and debugging capability using the on-board debugger.

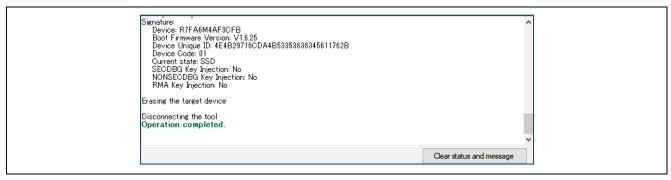

#### Initialize the MCU

This step is optional but recommended. Prior to downloading the example application, it is recommended to initialize the device to the SSD state. Unlocked flash content will be erased during this process. This step can be achieved using the Renesas Device Partition Manager or RFP. This is particularly helpful if the device was previously used in the NSECSD state or has a certain flash block locked up temporarily.

For instructions on how to use RFP to perform this function, see section 6.1.

Use Renesas Device Partition Manager and J-Link Debugger to initialize the MCU.

Establish the following connection prior to using the Renesas Device Partition Manager and the Onboard J-Link debugger to perform **Initialize device back to factory default**. Note that **Initialize device back to factory default** performs the same functionality as **Initialize Device** when using RFP:

- EK-RA6M4 jumper setting: J6 closed, J9 open. Other jumpers keep out-of-box setting.

- USB cable connected between J10 and development PC.

Note: You must power cycle the board prior to working with the Renesas Device Partition Manager after a debug session if using J-Link as connection interface.

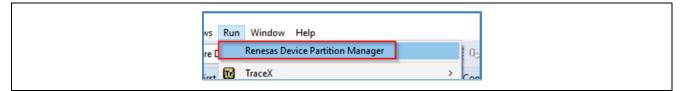

#### **Open Renesas Device Partition Manager**

Figure 53. Open the Renesas Device Partition Manager

Next, check Initialize device back to factory default, choose the connection method, then click Run.

Figure 54. Initialize RA6M4 using Renesas Device Partition Manager

After the MCU is initialized, proceed to the project importing and verification based on the IDE selected.

## 5.4 Example Application with e<sup>2</sup> studio IDE using Split Project Development Model

The e<sup>2</sup> studio project utilizes the Split Project Development Model to establish an application for IP protection. The assumption is that the Secure and Non-secure applications are developed by separate teams.

## 5.4.1 Import, Build, and Program the Secure Binary and Dummy Non-secure Binary

Use the following steps to provision the MCU with the Secure binary and a dummy Non-secure binary.

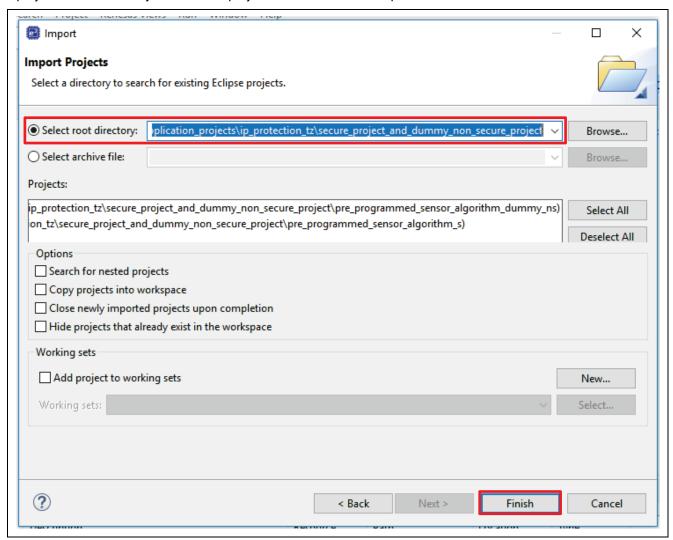

## 5.4.1.1 Import the Secure Project and Dummy Non-secure Project

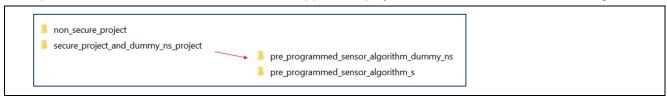

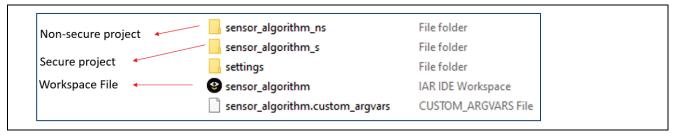

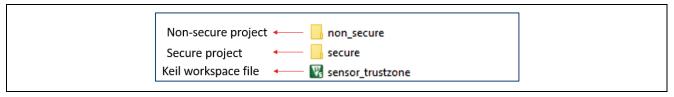

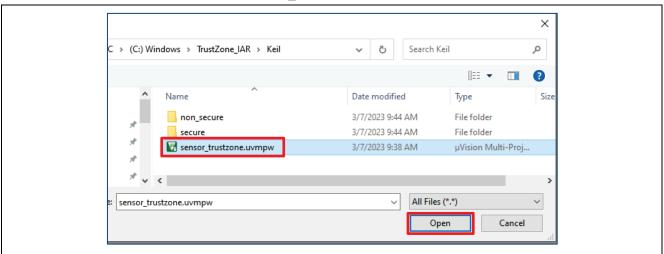

Unzip e2studio.zip, which is included in this application project, to reveal the folders shown in Figure 55.

Figure 55. e2studio Software Project Content

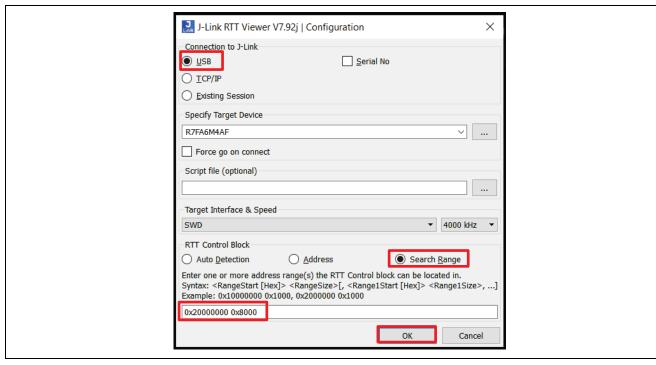

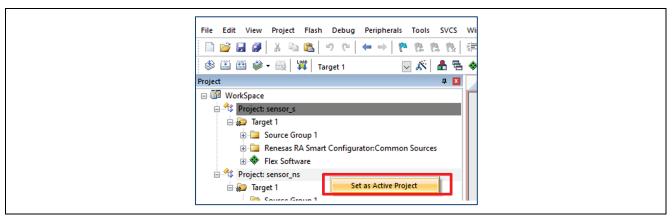

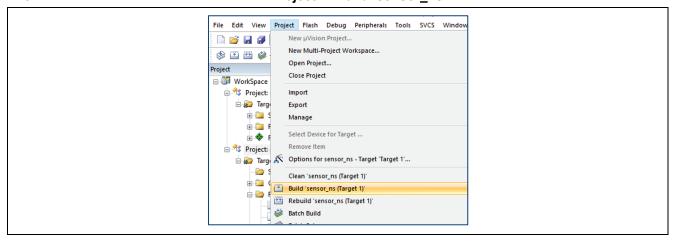

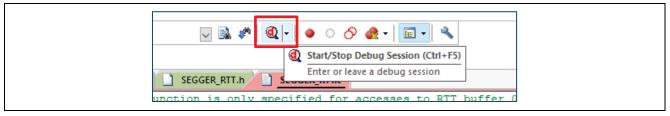

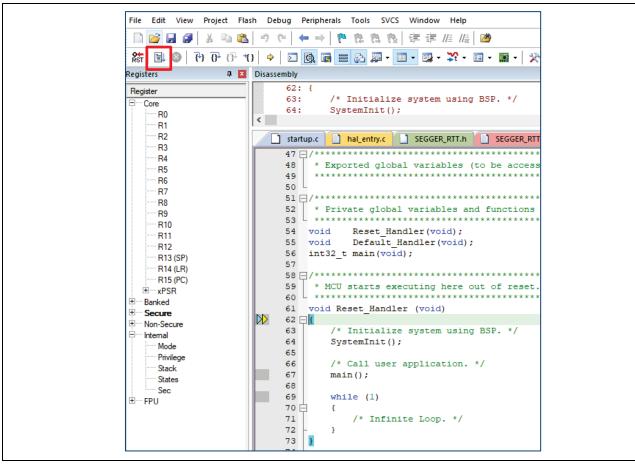

Next, follow <u>FSP User's Manual</u> section, <u>Importing an Existing Project into e2 studio</u> to import the Secure project and the dummy Non-secure project into the same workspace.