### **Description**

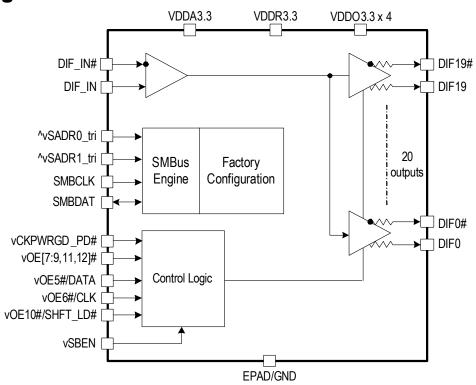

The 9QXL2001B is a 20-output very-low-additive phase jitter fanout buffer for PCIe Gen4, Gen5 and UPI applications. The 9QXL2001B provides two methods to control output enables; standard OE# pins and SMBus enable bits, or a simple 3-wire serial interface that is independent of the SMBus. The OE Control Mode is set via a hardware strap. It offers integrated terminations for  $85\Omega$  transmission lines.

# **PCIe Clocking Architectures**

- Common Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

# Typical Applications

Servers, Storage, Networking, Accelerators

# **Key Specifications**

- Output-to-output skew: < 50ps</li>

- Additive phase jitter: DB2000Q < 25fs rms</li>

- Additive phase jitter: PCle Gen4 < 40fs rms</li>

- Additive phase jitter: PCle Gen5 < 20fs rms</li>

#### **Features**

- Two Output Enable Control modes:

- Traditional 8 OE# pins allow hardware control of 8 outputs and 20 SMBus bits allow software control of each output

- Simple 3-wire Side-Band Interface allows real-time control of all 20 outputs

- Outputs remain Low/Low when powered up with floating input clock

- Low-Power HCSL (LP-HCSL) outputs:

- Zo = 85Ω outputs eliminate 80 resistors, saving 130mm<sup>2</sup> of area

- Power consumption reduced by 50%

- Nine selectable SMBus addresses

- Spread spectrum compatible

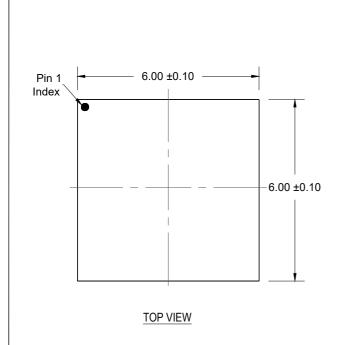

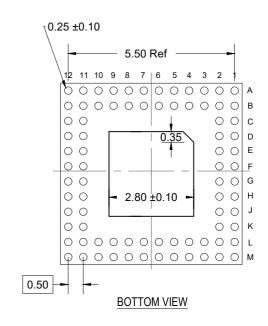

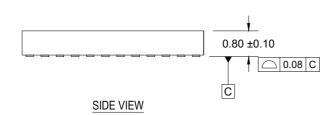

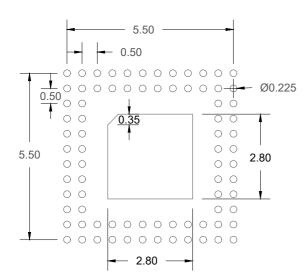

- 6 × 6 mm dual-row 80-VFQFPN

# **Output Features**

20 Low-Power HCSL (LP-HCSL) 85Ω output pairs

# **Block Diagram**

## **Contents**

| Description                                   |

|-----------------------------------------------|

| PCIe Clocking Architectures                   |

| Typical Applications                          |

| Key Specifications                            |

| Features                                      |

| Output Features                               |

| Block Diagram                                 |

| Pin Assignments                               |

| Pin Descriptions                              |

| Output Control                                |

| Power Management                              |

| Output Enable Control on 9QXL2001B (DB2000QL) |

| Traditional Method                            |

| Side-Band Interface                           |

| Absolute Maximum Ratings                      |

| Thermal Characteristics                       |

| Electrical Characteristics                    |

| Test Loads                                    |

| Alternate Terminations                        |

| SMBus Addressing                              |

| General SMBus Serial Interface Information    |

| How to Write                                  |

| How to Read                                   |

| Package Outline Drawings                      |

| Marking Diagram                               |

| Ordering Information                          |

| Revision History                              |

# **Pin Assignments**

Figure 1. Pin Assignments for 6 × 6 mm 80-VFQFPN Package – Top View

| · | 1       | 2       | 3     | 4            | 5                                        | 6                 | 7      | 8            | 9     | 10        | 11                   | 12     | _ |

|---|---------|---------|-------|--------------|------------------------------------------|-------------------|--------|--------------|-------|-----------|----------------------|--------|---|

| Α | DIF17   | DIF16#  | DIF16 | DIF15#       | DIF15                                    | DIF14#            | DIF14  | DIF13#       | DIF13 | DIF12#    | DIF12                | DIF11# | Α |

| В | DIF17#  | VDDO3.3 | NC    | ^v SADR0_tri | NC                                       | VDDA3.3           | NC     | ^v SADR1_tri | NC    | vOE12#    | VDDO3.3              | DIF11  | В |

| С | DIF18   | NC      |       |              |                                          |                   |        |              |       |           | vOE11#               | DIF10# | С |

| D | DIF18#  | NC      |       |              |                                          |                   |        |              |       |           | NC                   | DIF10  | D |

| Ε | DIF19   | vSBEN   |       |              |                                          |                   |        |              |       |           | v OE10#/SHF<br>T_LD# | vOE9#  | E |

| F | DIF19#  | NC      |       |              | 9QXL2001<br>6 x 6 mm, x 0.5mm pitch      |                   |        |              |       |           | NC                   | DIF9#  | F |

| G | DIF_IN  | NC      |       |              | 80-VFQFPN Package  Top View  EPAD is GND |                   |        |              |       |           | NC                   | DIF9   | G |

| Н | DIF_IN# | VDDR3.3 |       |              |                                          | CPAUI             | S GIND |              |       |           | v OE8#               | DIF8#  | Н |

| J | DIF0    | NC      |       |              |                                          |                   |        |              |       |           | NC                   | DIF8   | J |

| K | DIF0#   | NC      |       |              |                                          |                   |        |              |       | -         | vOE7#                | DIF7#  | K |

| L | DIF1    | VDDO3.3 | NC    | SMBDAT       | SMBCLK                                   | NC                | NC     | v OE5#/DATA  | NC    | vOE6#/CLK | VDDO3.3              | DIF7   | L |

| М | DIF1#   | DIF2    | DIF2# | DIF3         | DIF3#                                    | v CKPWRGD<br>_PD# | DIF4   | DIF4#        | DIF5  | DIF5#     | DIF6                 | DIF6#  | M |

|   | 1       | 2       | 3     | 4            | 5                                        | 6                 | 7      | 8            | 9     | 10        | 11                   | 12     | - |

Note: Pins with ^ prefix have internal pull-up resistor.

Pins with v prefix have internal pull-down resistor.

Pins with ^v prefix have internal pull-up/pull-down resistor network biasing input to VDD/2.

# **Pin Descriptions**

**Table 1. Pin Descriptions**

| Nun | nber | Name        | Туре   | Description                                                                                                                                                                                                                               |

|-----|------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α   | 1    | DIF17       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 2    | DIF16#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| Α   | 3    | DIF16       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 4    | DIF15#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| Α   | 5    | DIF15       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 6    | DIF14#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| Α   | 7    | DIF14       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 8    | DIF13#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| Α   | 9    | DIF13       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 10   | DIF12#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| Α   | 11   | DIF12       | Output | Differential true clock output.                                                                                                                                                                                                           |

| Α   | 12   | DIF11#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| В   | 1    | DIF17#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| В   | 2    | VDDO3.3     | Power  | Power supply for outputs. Nominally 3.3V.                                                                                                                                                                                                 |

| В   | 3    | NC          | -      | No connection.                                                                                                                                                                                                                            |

| В   | 4    | ^vSADR0_tri | Input  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus addresses. It has internal pull-up/down resistors to bias to $V_{DD}/2$ . See the SMBus Address Selection table. |

| В   | 5    | NC          | -      | No connection.                                                                                                                                                                                                                            |

| В   | 6    | VDDA3.3     | Power  | 3.3V power for the PLL core.                                                                                                                                                                                                              |

| В   | 7    | NC          | -      | No connection.                                                                                                                                                                                                                            |

| В   | 8    | ^vSADR1_tri | Input  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus addresses. It has internal pull-up/down resistors to bias to VDD/2. See the SMBus Address Selection table.       |

| В   | 9    | NC          | -      | No connection.                                                                                                                                                                                                                            |

| В   | 10   | vOE12#      | Input  | Active low input for enabling output 12. This pin has an internal pull-down.  1 = disable output, 0 = enable output.                                                                                                                      |

| В   | 11   | VDDO3.3     | Power  | Power supply for outputs. Nominally 3.3V.                                                                                                                                                                                                 |

| В   | 12   | DIF11       | Output | Differential true clock output.                                                                                                                                                                                                           |

| С   | 1    | DIF18       | Output | Differential true clock output.                                                                                                                                                                                                           |

| С   | 2    | NC          | -      | No connection.                                                                                                                                                                                                                            |

| С   | 11   | vOE11#      | Input  | Active low input for enabling output 11. This pin has an internal pull-down.  1 = disable output, 0 = enable output.                                                                                                                      |

| С   | 12   | DIF10#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| D   | 1    | DIF18#      | Output | Differential complementary clock output.                                                                                                                                                                                                  |

| D   | 2    | NC          | -      | No connection.                                                                                                                                                                                                                            |

Table 1. Pin Descriptions (Cont.)

| Nun | nber | Name            | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D   | 11   | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D   | 12   | DIF10           | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                                                                                                                |

| Е   | 1    | DIF19           | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                                                                                                                |

| Е   | 2    | vSBEN           | Input  | Input that enables the Side-Band Interface for controlling output enables. This pin disables the output enable pins when asserted. It has an internal pull-down resistor.  0 = OE pins and SMBus enable bits control outputs, Side-band interface disabled.  1 = Side-Band Interface controls output enables, OE pins and SMBus enable bits are disabled.                                                                      |

| Е   | 11   | vOE10#/SHFT_LD# | Input  | Active low input for enabling output 10 or SHFT_LD# pin for the Side-Band Interface. Refer to the Side-Band Interface section for details. This pin has an internal pull-down.  OE mode: 1 = disable output, 0 = enable output.  Side-Band Mode: 1 = enable Side-Band Interface shift register, 0 = disable Side-Band Interface shift register. A falling edge transfers Side-Band shift register contents to output register. |

| Е   | 12   | vOE9#           | Input  | Active low input for enabling output 9. This pin has an internal pull-down.  1 = disable output, 0 = enable output.                                                                                                                                                                                                                                                                                                            |

| F   | 1    | DIF19#          | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                       |

| F   | 2    | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F   | 11   | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F   | 12   | DIF9#           | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                       |

| G   | 1    | DIF_IN          | Input  | HCSL true input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| G   | 2    | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G   | 11   | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G   | 12   | DIF9            | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                                                                                                                |

| Н   | 1    | DIF_IN#         | Input  | HCSL complementary input.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Н   | 2    | VDDR3.3         | Power  | Power supply for differential input clock (receiver). This V <sub>DD</sub> should be treated as an analog power rail and filtered appropriately. Nominally 3.3V.                                                                                                                                                                                                                                                               |

| Н   | 11   | vOE8#           | Input  | Active low input for enabling output 8. This pin has an internal pull-down.  1 = disable output, 0 = enable output.                                                                                                                                                                                                                                                                                                            |

| Н   | 12   | DIF8#           | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                       |

| J   | 1    | DIF0            | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                                                                                                                |

| J   | 2    | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J   | 11   | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J   | 12   | DIF8            | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                                                                                                                |

| K   | 1    | DIF0#           | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                       |

| K   | 2    | NC              | -      | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| K   | 11   | vOE7#           | Input  | Active low input for enabling output 7. This pin has an internal pull-down.  1 = disable output, 0 = enable output.                                                                                                                                                                                                                                                                                                            |

Table 1. Pin Descriptions (Cont.)

| Number |    | Name         | Type   | Description                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|--------|----|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| K      | 12 | DIF7#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| L      | 1  | DIF1         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| L      | 2  | VDDO3.3      | Power  | Power supply for outputs. Nominally 3.3V.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| L      | 3  | NC           | N/A    | No connection.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 4  | SMBDAT       | I/O    | Data pin of SMBUS circuitry.                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| L      | 5  | SMBCLK       | Input  | Clock pin of SMBUS circuitry.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| L      | 6  | NC           | -      | o connection.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| L      | 7  | NC           | -      | No connection.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 8  | vOE5#/DATA   | Input  | Active low input for enabling output 5 or the data pin for the Side-Band Interface.  Refer to the Side-Band Interface section for details. This pin has an internal pull-down.  OE mode: 1 = disable output, 0 = enable output.  Side-Band mode: Data pin.                                                                                  |  |  |  |  |

| L      | 9  | NC           | -      | No connection.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 10 | vOE6#/CLK    | Input  | Active low input for enabling output 6 or the clock pin for the Side-Band Interface shift register. Refer to the Side-Band Interface section for details. This pin has an internal pull-down.  OE mode: 1 = disable output, 0 = enable output.  Side Band mode: Clocks data into the Side-Band Interface shift register on the rising edge. |  |  |  |  |

| L      | 11 | VDDO3.3      | Power  | Power supply for outputs. Nominally 3.3V.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| L      | 12 | DIF7         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 1  | DIF1#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| М      | 2  | DIF2         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 3  | DIF2#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| М      | 4  | DIF3         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 5  | DIF3#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| М      | 6  | vCKPWRGD_PD# | Input  | Input notifies device to sample latched inputs and start up on first high assertion. Low enters Power Down mode, subsequent high assertions exit Power Down mode. This pin has internal pull-down resistor.                                                                                                                                 |  |  |  |  |

| М      | 7  | DIF4         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 8  | DIF4#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| М      | 9  | DIF5         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 10 | DIF5#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| М      | 11 | DIF6         | Output | Differential true clock output.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| М      | 12 | DIF6#        | Output | Differential complementary clock output.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| -      | -  | EPAD         | GND    | Connect EPAD to ground.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# **Output Control**

Table 2. Output Control (SBEN = 0)

|             |         | Traditional Int   | erface   | Side Band Inter  | Outputs |         |

|-------------|---------|-------------------|----------|------------------|---------|---------|

| CKPWRGD_PD# | DIF_IN  | OEx bit Byte[2:0] | OEx# Pin | MASKx Byte[10:8] | Qx      | DIFx    |

| 0           | X       | X                 | Х        | X                | Х       | Low/Low |

|             |         | 0                 | Х        | Х                | Х       | Low/Low |

| 1           | Running | 1                 | 0        | X                | Х       | Running |

|             |         | 1                 | 1        | X                | Х       | Low/Low |

| 1           | Stannad | Otenned 1         |          | X                | Х       | Stopped |

|             | Stopped | 1                 | 1        | X                | Х       | Low/Low |

Table 3. Output Control (SBEN = 1)

|             |         | Traditional Int            | erface | Side Band Inter  | Outputs |         |

|-------------|---------|----------------------------|--------|------------------|---------|---------|

| CKPWRGD_PD# | DIF_IN  | OEx bit Byte[2:0] OEx# Pin |        | MASKx Byte[10:8] | Qx      | DIFx    |

| 0           | Х       | Х                          | Х      | Х                | Х       | Low/Low |

|             |         | Х                          | Х      | 0                | 0       | Low/Low |

| 1           | Running | Х                          | Х      | 0                | 1       | Running |

|             |         | Х                          | Х      | 1                | Х       | Running |

|             |         | Х                          | Х      | 0                | 0       | Low/Low |

| 1           | Stopped | Х                          | Х      | 0                | 1       | Stopped |

|             |         | Х                          | Х      | 1                | Х       | Stopped |

# **Power Management**

**Table 4. Power Connections**

| Pin N            | Pin Number |             |  |  |  |  |

|------------------|------------|-------------|--|--|--|--|

| V <sub>DD</sub>  | GND        | Description |  |  |  |  |

| B6, H2           | EPAD       | Analog      |  |  |  |  |

| B2, B11, L2, L11 | EPAD       | Outputs     |  |  |  |  |

# **Output Enable Control on 9QXL2001B (DB2000QL)**

#### **Traditional Method**

The 20-output 9QXL2001B has two methods for enabling and disabling outputs. The first is the traditional method of OE# pins and SMBus output enable bits. Outputs 5 through 12 have dedicated output enable pins and each of the 20 outputs have dedicated SMBus output enable bits in Bytes[0:2] of the SMBus register set.

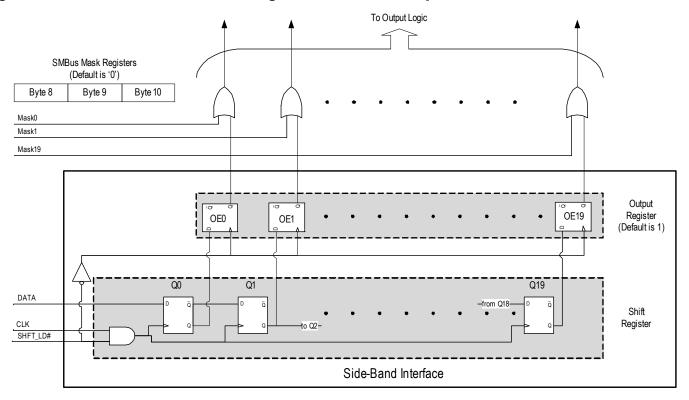

#### **Side-Band Interface**

The second method is a simple 3-wire serial interface referred to as the Side-Band Interface (SBI). This interface consists of DATA, CLK and SHFT\_LD# pins. When the SHFT\_LD# pin is high, the rising edge of CLK can shift DATA into the shift register. After shifting data, the falling edge of SHFT\_LD# clocks the shift register contents to the Output register.

Both the SBI and the traditional interface feed common output enable/disable synchronization logic ensuring glitch free enable and disable of outputs, regardless of the method used.

Both interfaces are not active at the same time, and the SBEN pin selects which interface is active. Tying the SBEN high enables the SBI. Tying the SBEN pin low enables the traditional OE# pin/SMBus output enable interface. When the SBI is enabled, OE[7:9, 11,12]# are disabled and DATA, CLK and SHFT\_LD# are enabled on OE5#, OE6# and OE10# respectively. Additionally, SMBus registers for masking off the disable function of the shift register (0 value of a bit) become active. When set to a one, the mask register forces its respective output to 'enabled'. This prevents accidentally disabling critical outputs when using the SBI.

An SMBus read back bit in Byte 4 indicates which output enable control interface is enabled.

When the SBI is enabled, and power has been applied, the SBI is active, even if the CKPWRGD\_PD# pin indicates the part is in power down. This allows loading the shift register and transferring the contents to the output register before the assertion of CKPWRGD. Note that the mask registers are part of the normal SMBus interface and cannot be accessed when the CKPWRGD\_PD# is low. Figure 1 provides a functional description of the SBI.

The SBI and the traditional SMBus output enable registers both default to the 'output enabled' state at power-up. The mask registers default to zero at power-up, allowing the shift register bits to disable their respective output. See Figure 2.

Figure 2. Side Band Interface Control Logic - Functional Description

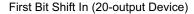

Figure 3 shows the basic timing of the side-band interface. The SHFT\_LD# pin goes high to enable the CLK input. Next, the rising edge of CLK clocks enable DATA into the shift register. After the 20th clock, stop the clock low and drive the SHFT\_LD# pin low. The falling edge of SHFT\_LD# clocks the shift register contents to the output register, enabling or disabling the outputs. Always shift 20 bits of data into the shift register to control the outputs.

Figure 3. Side Band Interface Functional Timing

The SBI interface supports clock rates up to 25MHz. Multiple devices may share CLK and DATA pins. Dedicating a SHFT\_LD# pin to each devices allows its use as a chip-select pin. When the SHFT\_LD# pin is low, the 9QXL2001 ignores any activity on the CLK and DATA pins.

# **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the 9QXL2001B at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 5. Absolute Maximum Ratings**

| Parameter            | Symbol             | Conditions                              | Minimum   | Typical | Maximum               | Unit | Notes |

|----------------------|--------------------|-----------------------------------------|-----------|---------|-----------------------|------|-------|

| Supply Voltage       | $V_{DDx}$          |                                         | -         | -       | 3.9                   | V    | 1,2   |

| Input Low Voltage    | V <sub>IL</sub>    |                                         | GND - 0.5 | -       | -                     | V    | 1     |

| Input High Voltage   | V <sub>IH</sub>    | Except for SMBus interface.             | -         | -       | V <sub>DD</sub> + 0.5 | V    | 1,3   |

| Input High Voltage   | V <sub>IHSMB</sub> | SMBus clock and data pins.              | -         | -       | 3.9                   | V    | 1     |

| Storage Temperature  | T <sub>S</sub>     |                                         | -65       | -       | 150                   | °C   | 1     |

| Junction Temperature | T <sub>J</sub>     | Maximum operating junction temperature. | -         | -       | 125                   | °C   | 1     |

| Input ESD Protection | ESD Prot           | Human Body Model.                       | 2500      | -       | -                     | V    | 1     |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

### **Thermal Characteristics**

**Table 6. Thermal Characteristics**

| Parameter                                         | Symbol                | Conditions                       | Package | Typical Value | Unit | Notes |

|---------------------------------------------------|-----------------------|----------------------------------|---------|---------------|------|-------|

|                                                   | $\theta_{JC}$         | Junction to case.                |         | 44            | °C/W | 1     |

|                                                   | $\theta_{Jb}$         | Junction to base.                |         | 2             | °C/W | 1     |

| $\theta_{\text{JA0}}$ Junction to air, still air. | 33                    | °C/W                             | 1       |               |      |       |

| Thermal Resistance                                | $\theta_{JA1}$        | Junction to air, 1 m/s air flow. | NHG80   | 29            | °C/W | 1     |

|                                                   | $\theta_{JA3}$        | Junction to air, 3 m/s air flow. |         | 28            | °C/W | 1     |

|                                                   | $\theta_{\text{JA5}}$ | Junction to air, 5 m/s air flow. |         | 27            | °C/W | 1     |

<sup>&</sup>lt;sup>1</sup> EPAD soldered to board.

<sup>&</sup>lt;sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>&</sup>lt;sup>3</sup> Not to exceed 3.9V.

### **Electrical Characteristics**

$T_A = T_{AMB}$ . Supply voltages per normal operation conditions; see Test Loads for loading conditions.

Table 7. SMBus

| Parameter                 | Symbol              | Conditions                                        | Minimum | Typical | Maximum         | Unit | Notes |

|---------------------------|---------------------|---------------------------------------------------|---------|---------|-----------------|------|-------|

| SMBus Input Low Voltage   | V <sub>ILSMB</sub>  |                                                   | -       | -       | 0.8             | V    | -     |

| SMBus Input High Voltage  | V <sub>IHSMB</sub>  |                                                   | 2.1     | -       | $V_{\rm DDSMB}$ | V    | -     |

| SMBus Output Low Voltage  | V <sub>OLSMB</sub>  | At I <sub>PULLUP.</sub>                           | -       | -       | 0.4             | V    | -     |

| SMBus Sink Current        | I <sub>PULLUP</sub> | At V <sub>OL.</sub>                               | 4       | -       | -               | mA   | -     |

| Nominal Bus Voltage       | $V_{\rm DDSMB}$     |                                                   | 2.7     | -       | 3.6             | V    | 1     |

| SCLK/SDATA Rise Time      | t <sub>RSMB</sub>   | (Max $V_{IL}$ - 0.15V) to (Min $V_{IH}$ + 0.15V). | -       | -       | 1000            | ns   | 1     |

| SCLK/SDATA Fall Time      | t <sub>FSMB</sub>   | (Min $V_{IH}$ + 0.15V) to (Max $V_{IL}$ - 0.15V). | -       | -       | 300             | ns   | 1     |

| SMBus Operating Frequency | f <sub>SMB</sub>    | SMBus operating frequency.                        | -       | -       | 400             | kHz  | 5     |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

Table 8. DIF\_IN Clock Input Parameters

| Parameter                           | Symbol             | Conditions                                                    | Minimum | Typical | Maximum | Unit | Notes |

|-------------------------------------|--------------------|---------------------------------------------------------------|---------|---------|---------|------|-------|

| Input Crossover Voltage –<br>DIF_IN | V <sub>CROSS</sub> | Crossover voltage.                                            | 100     | -       | 900     | mV   | 1     |

| Input Swing – DIF_IN                | V <sub>SWING</sub> | Differential value.                                           | 200     | -       | -       | mV   | 1     |

| Input Slew Rate – DIF_IN            | dv/dt              | Measured differentially.                                      | 0.7     | -       | -       | V/ns | 1,2   |

| Input Leakage Current               | I <sub>IN</sub>    | $CLK_IN\#$ , $V_{IN} = 0.8V$ , $CLK_IN$ , $V_{IN} = V_{DD}$ . | -150    | -       | 40      | μΑ   | -     |

| Input Duty Cycle                    | $d_{tin}$          | Measurement from differential waveform.                       | 45      | -       | 55      | %    | 1     |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

Table 9. Input/Supply/Common Parameters

| Parameter                        | Symbol                                     | Conditions                                           | Minimum   | Typical | Maximum               | Unit | Notes |

|----------------------------------|--------------------------------------------|------------------------------------------------------|-----------|---------|-----------------------|------|-------|

| Supply Voltage                   | V <sub>DDx</sub>                           | Supply voltage for core and analog.                  | 3.135     | 3.3     | 3.465                 | V    | -     |

| Ambient Operating<br>Temperature | T <sub>AMB</sub>                           | Industrial range.                                    | -40       | 25      | 85                    | °C   | -     |

| Input High Voltage               | V <sub>IH</sub>                            | Single-ended inputs, except SMBus, tri-level inputs. | 2         | -       | V <sub>DD</sub> + 0.3 | V    | -     |

| Input Low Voltage                | Single-ended inputs except SMRus tri-level |                                                      | GND - 0.3 | -       | 0.8                   | V    | -     |

<sup>&</sup>lt;sup>2</sup> Control input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup> Time from deassertion until outputs are > 200mV.

<sup>&</sup>lt;sup>4</sup> DIF\_IN input.

$<sup>^{5}</sup>$  The device must be powered up with CKPWRGD\_PD# = '1' for the SMBus to be active.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through ±75mV window centered around differential zero.

Table 9. Input/Supply/Common Parameters (Cont.)

| Parameter                                                               | Symbol                | Conditions                                                                                                                                   | Minimum   | Typical            | Maximum               | Unit   | Notes |

|-------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|-----------------------|--------|-------|

| Input High Voltage                                                      | V <sub>IH</sub>       | Tri-level inputs.                                                                                                                            | 2.2       | -                  | V <sub>DD</sub> + 0.3 | V      | -     |

| Input Mid Voltage                                                       | V <sub>IM</sub>       | Tri-level inputs.                                                                                                                            | 1.2       | V <sub>DD</sub> /2 | 1.8                   | V      | -     |

| Input Low Voltage                                                       | V <sub>IL</sub>       | Tri-level inputs.                                                                                                                            | GND - 0.3 | -                  | 0.8                   | V      | -     |

|                                                                         | I <sub>IN</sub>       | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = V_{DD}$ .                                                                                    | -5        | -                  | 5                     | μA     | -     |

| Input Current I <sub>INP</sub>                                          |                       | Single-ended inputs. $V_{IN}$ = 0 V; inputs with internal pull-up resistors. $V_{IN}$ = $V_{DD}$ ; inputs with internal pull-down resistors. | -50       | -                  | 50                    | μА     | -     |

| Input Frequency                                                         | F <sub>IN</sub>       | V <sub>DD</sub> = 3.3V.                                                                                                                      | 1         | -                  | 400                   | MHz    | -     |

| Pin Inductance                                                          | L <sub>pin</sub>      |                                                                                                                                              | -         | -                  | 7                     | nΗ     | 1     |

|                                                                         | C <sub>IN</sub>       | Logic inputs, except DIF_IN.                                                                                                                 | 1.5       | -                  | 5                     | pF     | 1     |

| Capacitance                                                             | C <sub>INDIF_IN</sub> | DIF_IN differential clock inputs.                                                                                                            | 1.5       | -                  | 2.7                   | pF     | 1,4   |

| •                                                                       | C <sub>OUT</sub>      | Output pin capacitance.                                                                                                                      | -         | -                  | 6                     | pF     | 1     |

| Clk Stabilization                                                       | T <sub>STAB</sub>     | From V <sub>DD</sub> power-up and after input clock stabilization or de-assertion of PD# to 1st clock.                                       | -         | 1.0                | 1.8                   | ms     | 1,2   |

| OE# Latency t <sub>LATOE#</sub>                                         |                       | DIF start after OE# assertion. DIF stop after OE# deassertion.                                                                               | 4         | 5                  | 10                    | clocks | 1,2,3 |

| Tdrive_PD# t <sub>DRVPD</sub> DIF output enable after PD# de-assertion. |                       | -                                                                                                                                            | 76        | 300                | μs                    | 1,3    |       |

| Tfall t <sub>F</sub> Fall time of control inputs.                       |                       | -                                                                                                                                            | -         | 5                  | ns                    | 2      |       |

| Trise t <sub>R</sub> Rise time of control inputs.                       |                       | -                                                                                                                                            | -         | 5                  | ns                    | 2      |       |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

Table 10. Side Band Interface

| Parameter           | Symbol              | Conditions                                                              | Minimum | Typical | Maximum | Unit   | Notes |

|---------------------|---------------------|-------------------------------------------------------------------------|---------|---------|---------|--------|-------|

| Clock Period        | t <sub>PERIOD</sub> | Clock period.                                                           | 40      | -       | -       | ns     | -     |

| Setup Time to Clock | t <sub>SETUP</sub>  | SHFT setup to CLK rising edge.                                          | 10      | -       | -       | ns     | -     |

| Data Setup Time     | t <sub>DSU</sub>    | DATA setup to CLK rising edge.                                          | 5       | -       | -       | ns     | -     |

| Data Hold Time      | t <sub>DHOLD</sub>  | DATA hold after CLK rising edge.                                        | 2       | -       | -       | ns     | 1     |

| Delay Time          | t <sub>DELAY</sub>  | Delay from CLK rising edge to LD# falling edge.                         | 10      | -       | -       | ns     | 1     |

| Propagation Delay   | t <sub>PD</sub>     | Delay from LD# falling edge to next output configuration taking effect. |         | -       | 10      | clocks | 3     |

| Slew Rate           | t <sub>SLEW</sub>   | CLK input (between 20% and 80%).                                        | 0.7     | -       | 6       | V/ns   | 2     |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Control input must be monotonic from 20% to 80% of input swing.

$<sup>^3</sup>$  Time from deassertion until outputs are > 200mV.

<sup>&</sup>lt;sup>4</sup> DIF\_IN input.

$<sup>^{2}\,\</sup>mathrm{Control}$  input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup> Refers to device differential input clock.

Table 11. LP-HCSL Outputs Driving High Impedance Receiver at 100MHz

| Parameter              | Symbol     | Conditions                                             | Minimum | Typical | Maximum | Industry<br>Limit | Unit | Notes   |

|------------------------|------------|--------------------------------------------------------|---------|---------|---------|-------------------|------|---------|

| Slew Rate              | dV/dt      | Scope averaging on, fast setting.                      | 2       | 2.4     | 3.5     | 2 to 4            | V/ns | 1,2,3   |

| Rise/Fall Matching     | ΔtR/tF     | Single-ended measurement.                              | -       | 4.8     | 15      | 20                | %    |         |

| Maximum Voltage        | Vmax       | Measurement on single ended                            | 700     | 800     | 900     | 660 to 1150       |      | 7,8     |

| Minimum Voltage        | Vmin       | signal using absolute value.<br>(scope averaging off). | -150    | -43     | 75      | -300 to +150      | mV   | 1,5,7,8 |

| Crossing Voltage (abs) | Vcross_abs | Scope averaging off.                                   | 250     | 391     | 550     | 250 to 550        | mV   | 1,6,7   |

| Crossing Voltage (var) | Δ-Vcross   | Scope averaging off.                                   | -       | 18      | 50      | 140               | mV   | 1,6,7   |

<sup>&</sup>lt;sup>1</sup> Confirmed by design and characterization, not 100% tested in production.

**Table 12. Current Consumption**

| Parameter                 | Symbol                  | Conditions                              | Minimum | Typical | Maximum | Unit |

|---------------------------|-------------------------|-----------------------------------------|---------|---------|---------|------|

| Operating Supply Current  | I <sub>DDVDD</sub>      | Source termination, all outputs 100MHz, | -       | 169     | 195     | mA   |

| Operating Supply Surferit | I <sub>DDVDDA/R</sub>   | $C_L = 2pF; Zo = 85\Omega.$             | -       | 5       | 6       | mA   |

| Powerdown Current         | I <sub>DDVDDPD</sub>    | All differential pairs low-low.         | -       | 1       | 2       | mA   |

| Fowerdown Current         | I <sub>DDVDDA/RPD</sub> | All differential pairs low-low.         | -       | 2       | 3       | mA   |

Table 13. Skew and Differential Jitter Parameters

| Parameter                                                                | Symbol                                                                                         | Conditions                         | Minimum | Typical | Maximum | Unit    | Notes       |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|---------|---------|---------|---------|-------------|

| CLK_IN, DIF[x:0]                                                         | t <sub>PD</sub>                                                                                | Input-to-output skew.              | 2.3     | 2.7     | 3.3     | ns      | 1,2,3,4,5,7 |

| CLK_IN, DIF[x:0]                                                         | t <sub>PDVARIATION</sub> Input-to-output skew variation for a given device at a given voltage. |                                    | -       | -       | 2       | ps/°C   | 1,2,3,5,8   |

| DIF[x:0] t <sub>SKEW_ALL</sub> Output-to-output skew across all outputs. |                                                                                                | -                                  | 35      | 50      | ps      | 1,2,3,7 |             |

| Duty Cycle Distortion                                                    | t <sub>DCD</sub>                                                                               | Measured differentially at 100MHz. | -0.5    | -0.2    | 0.5     | %       | 1,6,7       |

<sup>1</sup> Measured into fixed 2pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform.

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0 V. This results in a ±150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a ±75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>8</sup> Includes 300mV of overshoot for Vmax and 300mV of undershoot for Vmin.

<sup>&</sup>lt;sup>2</sup> Measured from differential cross-point to differential cross-point.

<sup>&</sup>lt;sup>3</sup> All input-to-output specs refer to the timing between an input edge and the specific output edge created by it.

<sup>&</sup>lt;sup>4</sup> Measured with scope averaging on to find mean value.

<sup>&</sup>lt;sup>5</sup> Confirmed by design and characterization, not 100% tested in production.

Table 14. Filtered Phase Jitter Parameters - PCIe Common Clocked (CC) Architectures

| Parameter                 | Symbol                      | Conditions                                                                                 | Minimum | Typical | Maximum | Industry<br>Limits | Unit        | Notes   |

|---------------------------|-----------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|--------------------|-------------|---------|

|                           | t <sub>jphPCleG1-CC</sub>   | PCIe Gen1                                                                                  | -       | 0.2     | 5       |                    | ps<br>(p-p) | 1,2,3,4 |

|                           |                             | PCIe Gen2 Low Band<br>10kHz < f < 1.5MHz<br>(PLL BW of 5–16MHz or 8–5MHz,<br>CDR = 5MHz)   | -       | 0.004   | 0.005   |                    | ps<br>(rms) | 1,2,4,6 |

| Additive Phase<br>Jitter  | <sup>t</sup> jphPCleG2-CC   | PCIe Gen2 High Band 1.5MHz < f < Nyquist (50MHz) (PLL BW of 5–16MHz or 8–5MHz, CDR = 5MHz) | -       | 0.07    | 0.09    | Not<br>applicable  | ps<br>(rms) | 1,2,4,6 |

|                           | t <sub>jphPCleG3/4-CC</sub> | PCIe Gen3, Gen4<br>(PLL BW of 2–4MHz or 2–5MHz,<br>CDR = 10MHz)                            | -       | 0.03    | 0.04    |                    | ps<br>(rms) | 1,2,4,6 |

| <sup>t</sup> jphPCleG5-CC |                             | PCIe Gen5<br>(see PCIe Gen5 specifications for<br>details)                                 | -       | 0.01    | 0.02    |                    | ps<br>(rms) | 1,2,4,6 |

#### Table 15. Filtered Phase Jitter Parameters – PCIe Independent Reference (IR) Architectures

| Parameter    | Symbol                      | Conditions                                   | Minimum | Typical | Maximum | Industry<br>Limits | Unit        | Notes   |

|--------------|-----------------------------|----------------------------------------------|---------|---------|---------|--------------------|-------------|---------|

| Additive     | t <sub>jphPCleG2-SRIS</sub> | PCIe Gen2<br>(PLL BW of 16MHz, CDR = 5MHz)   | -       | 0.09    | 0.11    | Not                | ps<br>(rms) | 1,2,4,6 |

| Phase Jitter | tjphPCleG3-SRIS             | PCIe Gen3<br>(PLL BW of 2–4MHz, CDR = 10MHz) | -       | 0.02    | 0.03    | applicable         | ps<br>(rms) | 1,2,4,6 |

#### Notes on PCle Filtered Phase Jitter tables

<sup>&</sup>lt;sup>6</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>&</sup>lt;sup>7</sup> Measured from differential waveform.

<sup>&</sup>lt;sup>8</sup> This is the amount of input-to-output delay variation with respect to temperature. This is equivalent to 250ps over the -40°C to +85°C temperature range.

<sup>&</sup>lt;sup>1</sup> Applies to all differential outputs, confirmed by design and characterization.

<sup>&</sup>lt;sup>2</sup> Applies to all outputs when driven by a low phase noise source.

<sup>&</sup>lt;sup>3</sup> Sample size of at least 100K cycles. This figure extrapolates to 108ps pk-pk at 1M cycles for a BER of 1<sup>-12</sup>.

<sup>&</sup>lt;sup>4</sup> Additive jitter for RMS values is calculated by solving the following equation for b  $[b = sqrt(c^2 - a^2)]$  where "a" is rms input jitter and "c" is rms total jitter.

<sup>&</sup>lt;sup>5</sup> IR is the new name for Separate Reference Independent Spread (SRIS) and Separate Reference no Spread (SRNS) PCIe clock architectures. According to the PCIe Base Specification Rev4.0 version 1.0, the jitter transfer functions and corresponding jitter limits are not defined for the IR clock architecture. The IR filters from the PCIe Base Specification, Rev 3.1a are used to populate this table. There are no accepted filters or limits for IR clock architectures at PCIe Gen1 or Gen4 data rates at the time of publication.

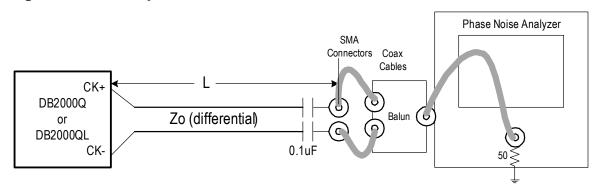

<sup>&</sup>lt;sup>6</sup> Measured using SMA100B signal source, or equivalent, and a phase noise analyzer.

Table 16. Filtered Phase Jitter Parameters - DB2000Q Filter

| Parameter                | Symbol                     | Conditions | Minimum | Typical | Maximum | Specification<br>Limit | Unit        | Notes |

|--------------------------|----------------------------|------------|---------|---------|---------|------------------------|-------------|-------|

| Additive<br>Phase Jitter | t <sub>jphDB2000Qadd</sub> | 100MHz     | -       | 23      | 25      | 80                     | fs<br>(rms) | 1,2,3 |

<sup>&</sup>lt;sup>1</sup> Measured using SMA100B signal source, or equivalent, and a phase noise analyzer.

Table 17. Unfiltered Phase Jitter Parameters - 12kHz to 20MHz

| Parameter             | Symbol                     | Conditions | Minimum | Typical | Maximum | Industry<br>Limits  | Unit     | Notes |

|-----------------------|----------------------------|------------|---------|---------|---------|---------------------|----------|-------|

| Additive Phase Jitter | <b>t</b>                   | 100MHz     | -       | 97      | 106     | Not                 | fc (rmc) | 1,2,3 |

| Additive Phase sitter | <sup>l</sup> jph12k-20Madd | 156.25MHz  | -       | 86      | 94      | applicable fs (rms) | 1,2,3    |       |

<sup>&</sup>lt;sup>1</sup> Measured using SMA100B signal source, or equivalent, and a phase noise analyzer.

### **Test Loads**

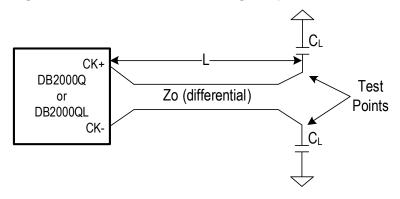

Figure 4. AC/DC Test Load for High Impedance Receivers

Figure 5. Test Setup for DB2000Q Additive Phase Jitter Measurement

<sup>&</sup>lt;sup>2</sup> After applying DB2000Q filter.

<sup>&</sup>lt;sup>3</sup> Additive jitter for RMS values is calculated by solving for b where  $[b = sqrt(c^2 - a^2)]$  where "a" is rms input jitter and "c" is rms total jitter.

<sup>&</sup>lt;sup>2</sup> 12kHz–20MHz brick wall filter.

<sup>&</sup>lt;sup>3</sup> Additive jitter for RMS values is calculated by solving for b where  $[b = sqrt(c^2 - a^2)]$  where "a" is rms input jitter and "c" is rms total jitter.

**Table 18. Parameters for Test Loads**

| Rs (Ω)   | Ζο (Ω) | L (cm) | C <sub>L</sub> (pF) |

|----------|--------|--------|---------------------|

| Internal | 85     | 25.4   | 2                   |

### **Alternate Terminations**

The LP-HCSL output can easily drive other logic families. See <u>"AN-891 Driving LVPECL, LVDS, and CML Logic with "Universal" Low-Power HCSL Outputs</u> for termination schemes for LVPECL, LVDS, CML and SSTL.

# **SMBus Addressing**

**Table 19. SMBus Address Selection**

| SADR(1:0)_tri | SMBus Address (Read/Write bit = 0) |

|---------------|------------------------------------|

| 00            | D8                                 |

| 0M            | DA                                 |

| 01            | DE                                 |

| MO            | C2                                 |

| MM            | C4                                 |

| M1            | C6                                 |

| 10            | CA                                 |

| 1M            | CC                                 |

| 11            | CE                                 |

### **General SMBus Serial Interface Information**

#### **How to Write**

- Controller (host) sends a start bit

- Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- Controller (host) sends the byte count = X

- Renesas clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- Renesas clock will acknowledge each byte one at a time

- Controller (host) sends a stop bit

|           | Index Blo | ock W  | Vrite Operation          |

|-----------|-----------|--------|--------------------------|

| Controll  | er (Host) |        | Renesas (Slave/Receiver) |

| Т         | starT bit |        |                          |

| Slave A   | Address   |        |                          |

| WR        | WRite     |        |                          |

|           |           |        | ACK                      |

| Beginning | Byte = N  |        |                          |

|           |           |        | ACK                      |

| Data Byte | Count = X |        |                          |

|           |           |        | ACK                      |

| Beginnin  | g Byte N  |        |                          |

|           |           |        | ACK                      |

| 0         |           |        |                          |

| 0         |           | X Byte | 0                        |

| 0         |           | te     | 0                        |

|           |           |        | 0                        |

| Byte N    | + X - 1   |        |                          |

|           |           |        | ACK                      |

| Р         | stoP bit  |        |                          |

#### **How to Read**

- Controller (host) will send a start bit

- Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address

- Renesas clock will acknowledge

- Renesas clock will send the data byte count = X

- Renesas clock sends Byte N+X-1

- Renesas clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

|     | Index Block Read Operation |        |                          |  |  |  |

|-----|----------------------------|--------|--------------------------|--|--|--|

| Co  | ntroller (Host)            |        | Renesas (Slave/Receiver) |  |  |  |

| Т   | starT bit                  |        |                          |  |  |  |

| S   | lave Address               |        |                          |  |  |  |

| WR  | WRite                      |        |                          |  |  |  |

|     |                            |        | ACK                      |  |  |  |

| Beg | inning Byte = N            |        |                          |  |  |  |

|     |                            |        | ACK                      |  |  |  |

| RT  | Repeat starT               |        |                          |  |  |  |

|     | lave Address               |        |                          |  |  |  |

| RD  | ReaD                       |        |                          |  |  |  |

|     |                            |        | ACK                      |  |  |  |

|     |                            |        |                          |  |  |  |

|     |                            |        | Data Byte Count=X        |  |  |  |

|     | ACK                        |        |                          |  |  |  |

|     |                            |        | Beginning Byte N         |  |  |  |

|     | ACK                        |        |                          |  |  |  |

|     |                            | ф      | 0                        |  |  |  |

|     | 0                          | X Byte | 0                        |  |  |  |

|     | 0                          |        | 0                        |  |  |  |

|     | 0                          |        |                          |  |  |  |

|     |                            |        | Byte N + X - 1           |  |  |  |

| N   | Not acknowledge            |        |                          |  |  |  |

| Р   | stoP bit                   |        |                          |  |  |  |

### SMBus Table: Output Enable Register (functional only when SBEN = 0)

| Byte 0 | Name      | Control Function | Туре | 0       | 1      | Default |  |

|--------|-----------|------------------|------|---------|--------|---------|--|

| Bit 7  |           | Reserved         |      |         |        |         |  |

| Bit 6  | DIF_19_En | Output Enable    | RW   | Low/Low | Enable | 1       |  |

| Bit 5  | DIF_18_En | Output Enable    | RW   | Low/Low | Enable | 1       |  |