#### ISL71030M

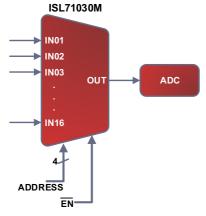

#### Radiation Tolerant 5V 16-Channel Analog Multiplexer

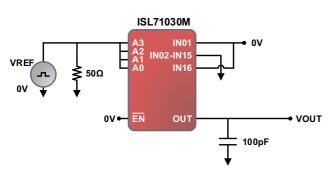

The <u>ISL71030M</u> is a radiation tolerant, 16-channel multiplexer that is fabricated using the proprietary P6 SOI process technology to provide excellent latch-up performance. It operates with a single supply range from 3V to 5.5V and has a 4-bit address line plus an enable that can be driven with adjustable logic thresholds to conveniently select one of 16 available channels. An inactive channel is separated from the active channel by a high impedance, which inhibits any interaction between the channels.

The ISL71030M low  $r_{DS(ON)}$  allows for improved signal integrity and reduced power losses. The ISL71030M is also designed for cold sparing and is excellent for redundancy in high reliability applications. It is designed to provide a high impedance to the analog source in a powered-off condition, making it easy to add additional backup devices without incurring extra power dissipation. The ISL71030M also has analog overvoltage protection on the input that disables the switch during an overvoltage event to protect upstream and downstream devices.

The ISL71030M is available in a 32 Ld TQFP and operates across the extended temperature range of -55°C to +125°C.

#### **Features**

- Fabricated using P6 SOI process technology

- · Rail-to-rail operation

- · No latch-up

- Low r<sub>DS(ON)</sub>: <120Ω (maximum)</li>

- Single supply operation: 3V to 5.5V

- Adjustable logic threshold control

- · Cold sparing capable: -0.4V to 7V

- Analog overvoltage range: -0.4V to 7V

- · Switch input off leakage: 120nA

- Transition times (t<sub>AHI</sub>): 70ns

- · Break-before-make switching

- ESD protection ≥5kV (HBM)

- · Passes NASA low outgassing specifications

- NiPdAu lead finish (Pb-free, Sn-free)

- Operating temperature range: -55°C to +125°C

- · Radiation tolerance

- o Low dose rate (0.01rad(Si)/s): 30krad(Si)

- $\circ$  SEL/SEB LET<sub>TH</sub> (V+ = 6.5V): 43MeV•cm<sup>2</sup>/mg

#### **Applications**

- · Telemetry signal processing

- · Harsh environments

- o Down-hole drilling

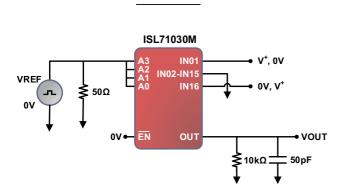

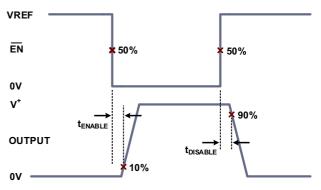

Figure 1. Typical Application

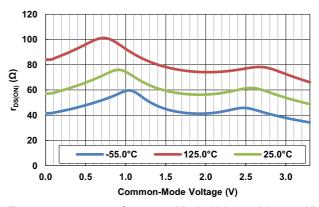

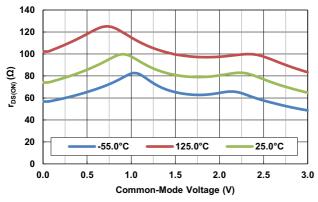

Figure 2.  $r_{DS(ON)}$  vs Common-Mode Voltage (V+ = 4.5V)

## ISL71030M

# **Contents**

| 1.  | Overview                                    | 3 |

|-----|---------------------------------------------|---|

| 1.1 | Ordering Information                        | 3 |

| 2.  | Pin Information                             | 4 |

| 2.1 | Pin Assignments                             | 4 |

| 2.2 | Pin Descriptions                            | 4 |

| 3.  | Specifications                              | 5 |

| 3.1 | Absolute Maximum Ratings                    | 5 |

| 3.2 | Thermal Information                         | 5 |

| 3.3 | Recommended Operating Conditions            | 5 |

| 3.4 | Electrical Specifications, V+ = 5V          | 5 |

| 3.5 | Electrical Specifications, V+ = 3.3V        | 7 |

| 3.6 | Truth Table                                 | 9 |

| 3.7 | Timing Diagrams                             | 9 |

| 4.  | Typical Performance Graphs                  | 1 |

| 5.  | Application Information                     | 4 |

| 5.1 | Power-Up Considerations                     | 4 |

| 5.2 | Overvoltage Protection                      | 4 |

| 5.3 | VREF and Logic Functionality                | 4 |

| 5.4 | Considerations for Redundant Applications14 | 4 |

| 6.  | Radiation Tolerance                         | 5 |

| 6.1 | Total Ionizing Dose (TID) Testing           | 5 |

| 6.2 | Single-Event Effects Testing                |   |

| 7.  | Revision History                            | 3 |

| 8.  | Package Outline Drawing                     | 4 |

ISL71030M 1. Overview

# 1. Overview

# 1.1 Ordering Information

| Part Number (Notes 2, 3) | Part Marking | Package Description<br>(RoHS Compliant) | Pkg. Dwg. # | Carrier Type<br>( <u>Note 1</u> ) | Temp. Range   |

|--------------------------|--------------|-----------------------------------------|-------------|-----------------------------------|---------------|

| ISL71030MNZ              | ISL7103 0MNZ | 32 Ld TQFP                              | Q32.5X5A    | -                                 | -55 to +125°C |

| ISL71030MNZ-T            |              |                                         |             | 1k                                |               |

| ISL71030MNZ-T7A          |              |                                         |             | 250                               |               |

#### Notes:

- 1. See <u>TB347</u> for details about reel specifications.

- 2. These Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the ISL71030M device page. For more information about MSL, see TB363.

ISL71030M 2. Pin Information

# 2. Pin Information

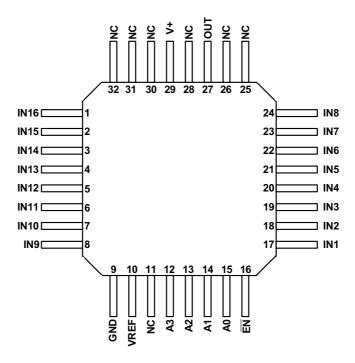

# 2.1 Pin Assignments

Top View

# 2.2 Pin Descriptions

| Pin Number                                                | ESD Circuit | Pin Name | Description                                   |

|-----------------------------------------------------------|-------------|----------|-----------------------------------------------|

| 1, 2, 3, 4, 5, 6, 7, 8, 17,<br>18, 19, 20, 21, 22, 23, 24 | 1           | INx      | Multiplexer input                             |

| 9                                                         | -           | GND      | Ground                                        |

| 10                                                        | 1           | VREF     | Reference voltage that sets logic thresholds. |

| 11, 25, 26, 28, 30, 31, 32                                | -           | NC       | Not electrically connected                    |

| 12, 13, 14, 15                                            | 1           | Ax       | Multiplexer address lines                     |

| 16                                                        | 1           | EN       | Multiplexer Enable control (active low).      |

| 27                                                        | 2           | OUT      | Multiplexer output                            |

| 29                                                        | 1           | V+       | Positive power supply                         |

|                                                           | 9V CI       | GND      | Pin # 9V Clamp 9V Clamp GND Circuit 2         |

# 3. Specifications

## 3.1 Absolute Maximum Ratings

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                         | Minimum   | Maximum | Unit |  |

|---------------------------------------------------|-----------|---------|------|--|

| Maximum Supply Voltage (V+ to GND)                |           | 7       | V    |  |

| Maximum Supply Voltage (V+ to GND) (Note 4)       |           | 6.5     | V    |  |

| Analog Input Voltage Range (INx)                  | -0.4      | 7       | V    |  |

| Digital Input Voltage Range (EN, Ax)              | GND - 0.4 | VREF    | V    |  |

| VREF to GND                                       |           | 7       | V    |  |

| ESD Rating                                        | Va        | alue    | Unit |  |

| Human Body Model (Tested per MIL-STD-883 TM 3015) |           | 5       |      |  |

| Charged Device Model (Tested per JS-002-2014)     | 5         | 500     | V    |  |

Note:

#### 3.2 Thermal Information

| Thermal Resistance (Typical)             | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|------------------------|------------------------|

| 32 Ld TQFP ( <u>Notes 5</u> , <u>6</u> ) | 61                     | 26                     |

Notes:

<sup>6.</sup> For  $\theta_{\text{JC}}$ , the "case temp" location is taken at the package top center.

| Parameter                              | Minimum | Maximum          | Unit |

|----------------------------------------|---------|------------------|------|

| Maximum Operating Junction Temperature |         | +150             | °C   |

| Pb-Free Reflow Profile                 |         | See <u>TB493</u> |      |

# 3.3 Recommended Operating Conditions

| Parameter                           | Minimum | Maximum | Unit |

|-------------------------------------|---------|---------|------|

| Supply Voltage, V <sub>CC</sub>     | 3       | 5.5     | V    |

| Ambient Operating Temperature Range | -55     | +125    | °C   |

| V <sub>REF</sub> to GND             | 3       | 5.5     | V    |

# 3.4 Electrical Specifications, V+ = 5V

Recommended operating conditions, GND = 0V,  $V_{REF}$  = 5V,  $V_{IL}$  = 5V,  $V_{IL}$  = 0V,  $T_A$  = +25°C, unless otherwise noted. **Boldface limits apply** across the operating temperature range, -55°C to +125°C; over at total ionizing dose of 30krad(Si) with exposure at a low dose rate of <43 MeV•cm<sup>2</sup>/mg.

| Parameter                                  | Symbol                | Test Conditions                                                        | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|--------------------------------------------|-----------------------|------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| Analog Input Signal Range                  | V <sub>IN</sub>       |                                                                        | 0                        |     | V+                       | ٧    |

| Channel On-Resistance                      | r <sub>DS(ON)</sub>   | V+ = 4.5V, V <sub>IN</sub> = 0V to V+<br>I <sub>OUT</sub> = 1mA        |                          | 40  | 120                      | Ω    |

| r <sub>DS(ON)</sub> Match Between Channels |                       | V+ = 4.5V, V <sub>IN</sub> = 0V, 2.25V, 4.5V<br>I <sub>OUT</sub> = 1mA |                          |     | 5                        | Ω    |

| On-Resistance Flatness                     | r <sub>FLAT(ON)</sub> | V+ = 4.5V, V <sub>IN</sub> = 0V to V+                                  |                          |     | 40                       | Ω    |

<sup>4.</sup> Tested in a heavy ion environment at LET=43 MeV•cm<sup>2</sup>/mg

<sup>5.</sup> θ<sub>JA</sub> is measured with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u>.

Recommended operating conditions, GND = 0V,  $V_{REF}$  = 5V,  $V_{IH}$  = 5V,  $V_{IL}$  = 0V,  $T_A$  = +25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range**, -55°C to +125°C; over at total ionizing dose of 30krad(Si) with exposure at a low dose rate of <43 MeV•cm<sup>2</sup>/mg. (Continued)

| Parameter                                                    | Symbol                            | Test Conditions                                                                                                              | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|--------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| Switch Input Off Leakage                                     | I <sub>IN(OFF)</sub>              | V+ = 5.5V, $V_{IN}$ = 5V, Unused inputs and $V_{OUT}$ = 0.5V                                                                 | -30                      |     | 30                       | nA   |

|                                                              |                                   | V+ = 5.5V, V <sub>IN</sub> = 0.5V, Unused inputs and V <sub>OUT</sub> = 5V                                                   | -30                      |     | 30                       | nA   |

| Switch Input Off Overvoltage Leakage                         | I <sub>IN(OFF-0V)</sub>           | V+ = 5.5V, $V_{IN}$ = 7V, Unused inputs and $V_{OUT}$ = 0V, $T_A$ = +25°C, -55°C                                             | -30                      |     | 30                       | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      | -30                      |     | 120                      | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -30                      |     | 30                       | nA   |

| Switch Input Off Leakage with Supply<br>Voltage Grounded     | I <sub>IN(POWER-OFF)</sub>        | $V_{IN} = 7V$ , $V_{OUT} = 0V$ , $V + = V_{EN} = V_{REF} = 0V$ , $T_A = +25^{\circ}C$ , $-55^{\circ}C$                       | -20                      |     | 20                       | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      | -20                      |     | 50                       | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -20                      |     | 20                       | nA   |

| Switch Input Off Leakage with Supply Voltage Open            | I <sub>IN(POWER-OFF)</sub>        | V <sub>IN</sub> = 7V, V <sub>OUT</sub> = 0V<br>V+ = V <sub>EN</sub> = V <sub>REF</sub> = Open, T <sub>A</sub> = +25°C, -55°C | -20                      |     | 20                       | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      | -20                      |     | 50                       | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -20                      |     | 20                       | nA   |

| Switch On Input Leakage with<br>Overvoltage Applied to Input | I <sub>IN(ON-0V)</sub>            | V+ = 5.5V, V <sub>IN</sub> = 7V, V <sub>OUT</sub> = OPEN                                                                     | 2.75                     |     | 5.50                     | μA   |

| Switch Output Off Leakage                                    | I <sub>OUT(OFF)</sub>             | V+ = 5.5V, V <sub>OUT</sub> = 5V, All inputs = 0.5V,<br>T <sub>A</sub> = +25°C, -55°C                                        | -30                      |     | 30                       | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      | 0                        |     | 150                      | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -30                      |     | 30                       | nA   |

|                                                              |                                   | V+ = 5.5V, V <sub>OUT</sub> = 0.5V, All inputs = 5V,<br>T <sub>A</sub> = +25°C, -55°C                                        | -30                      |     | 30                       | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -30                      |     | 30                       | nA   |

| Switch Output Leakage with Switch Enabled                    | I <sub>OUT(ON)</sub>              | V+ = 5.5V, V <sub>IN</sub> = V <sub>OUT</sub> = 5V<br>All unused inputs at 0.5V, T <sub>A</sub> = +25°C, -55°C               | -30                      |     | 30                       | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      | 0                        |     | 150                      | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -30                      |     | 30                       | nA   |

|                                                              |                                   | V+ = 5.5V, V <sub>IN</sub> = V <sub>OUT</sub> = 0.5V<br>All unused inputs at 5V                                              | -30                      |     | 30                       | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        | -30                      |     | 30                       | nA   |

| Logic Input Voltage High/Low                                 | V <sub>IH/L</sub>                 | V+ = 5.5V, V <sub>REF</sub> = 3.3V                                                                                           | 1.3                      |     | 1.6                      | ٧    |

| Input Current with V <sub>AH</sub> , V <sub>ENH</sub>        | I <sub>AH,</sub> I <sub>ENH</sub> | V+ = 5.5V, V <sub>EN</sub> = V <sub>A</sub> = V <sub>REF</sub>                                                               | -0.1                     |     | 0.1                      | μΑ   |

| Input Current with V <sub>AL</sub> , V <sub>ENL</sub>        | I <sub>AL,</sub> I <sub>ENL</sub> | V+ = 5.5V, V <sub>EN</sub> = V <sub>A</sub> = 0V                                                                             | -0.1                     |     | 0.1                      | μΑ   |

| Quiescent Supply Current                                     | I <sub>SUPPLY</sub>               | V+ = V <sub>REF</sub> = V <sub>EN</sub> = 5.5V<br>V <sub>A</sub> = 0V, T <sub>A</sub> = +25°C, -55°C                         |                          |     | 100                      | nA   |

|                                                              |                                   | T <sub>A</sub> = +125°C                                                                                                      |                          |     | 300                      | nA   |

|                                                              |                                   | Post radiation, +25°C                                                                                                        |                          |     | 300                      | nA   |

| Reference Quiescent Supply Current                           | I <sub>REF</sub>                  | $V+ = V_{REF} = V_{EN} = 5.5V$<br>$V_A = 0V$                                                                                 |                          |     | 200                      | nA   |

| Dynamic                                                      |                                   |                                                                                                                              |                          |     |                          |      |

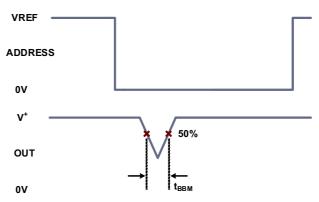

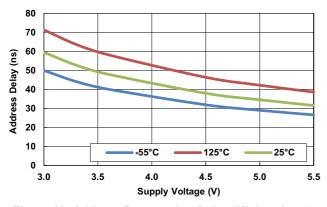

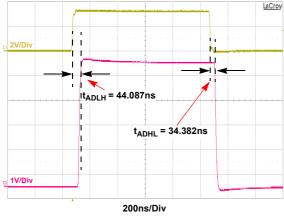

| Addressing Transition Time                                   | t <sub>AHL</sub>                  | V+ = 4.5V; <u>Figure 3</u>                                                                                                   | 10                       |     | 70                       | ns   |

Recommended operating conditions, GND = 0V,  $V_{REF}$  = 5V,  $V_{IL}$  = 5V,  $V_{IL}$  = 0V,  $T_A$  = +25°C, unless otherwise noted. **Boldface limits apply** across the operating temperature range, -55°C to +125°C; over at total ionizing dose of 30krad(Si) with exposure at a low dose rate of <43 MeV•cm²/mg. (Continued)

| Parameter               | Symbol                | Test Conditions                                                              | Min<br>(Note 7) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|-------------------------|-----------------------|------------------------------------------------------------------------------|-----------------|-----|--------------------------|------|

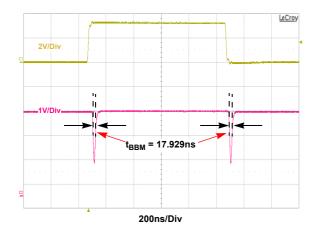

| Break-Before-Make-Delay | t <sub>BBM</sub>      | V+ = 4.5V; <u>Figure 7</u>                                                   | 5               | 18  | 40                       | ns   |

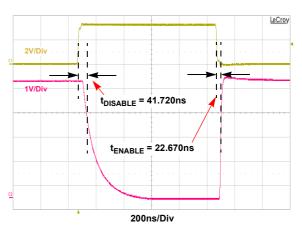

| Enable Turn-On Time     | t <sub>EN(ON)</sub>   | V+ = 4.5V; <u>Figure 5</u>                                                   |                 |     | 40                       | ns   |

| Enable Turn-Off Time    | t <sub>EN(OFF)</sub>  | V+ = 4.5V; <u>Figure 5</u>                                                   |                 |     | 40                       | ns   |

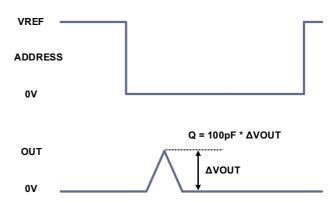

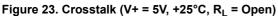

| Charge Injection        | V <sub>CTE</sub>      | C <sub>L</sub> = 100pF, V <sub>IN</sub> = 0V, <u>Figure 9</u>                |                 | 1.4 | 5                        | рС   |

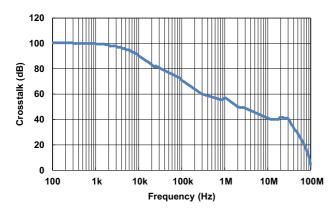

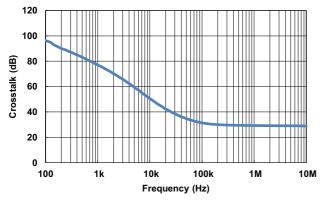

| Off Isolation           | V <sub>ISO</sub>      | V <sub>EN</sub> = V <sub>REF</sub> , R <sub>L</sub> = OPEN, f = 1kHz         | 60              |     |                          | dB   |

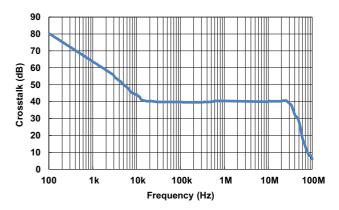

| Crosstalk               | V <sub>CT</sub>       | V <sub>EN</sub> = 0V, f = 1kHz, V <sub>P-P</sub> = 1V, R <sub>L</sub> = OPEN | 73              |     |                          | dB   |

| Input Capacitance       | C <sub>IN(OFF)</sub>  | f = 1MHz                                                                     |                 |     | 5                        | pF   |

| Output Capacitance      | C <sub>OUT(OFF)</sub> | f = 1MHz                                                                     |                 |     | 25                       | pF   |

# 3.5 Electrical Specifications, V+ = 3.3V

Recommended operating conditions, GND = 0V,  $V_{REF}$  = 3.3V,  $V_{IH}$  = 3.3V,  $V_{IL}$  = 0V,  $T_A$  = +25°C, unless otherwise noted. **Boldface limits** apply across the operating temperature range, -55°C to +125°C; over at total ionizing dose of 30 krad(Si) with exposure at a low dose rate of 43 MeV•cm²/mg.

| Parameter                                                        | Symbol                  | Test Conditions                                                                         | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| Analog Input Signal Range                                        | V <sub>IN</sub>         |                                                                                         | 0                        |     | V+                       | V    |

| Channel On-Resistance                                            | r <sub>DS(ON)</sub>     | V+ = 3V, V <sub>IN</sub> = 0V to V+, I <sub>OUT</sub> = 1mA                             | 25                       | 70  | 200                      | Ω    |

| r <sub>DS(ON)</sub> Match Between Channels                       | $\Delta r_{DS(ON)}$     | V+ = 3V, V <sub>IN</sub> = 0.5V, 2.5V, I <sub>OUT</sub> = 1mA                           |                          |     | 5                        | Ω    |

| On-Resistance Flatness                                           | r <sub>FLAT(ON)</sub>   | V+ = 3V, V <sub>IN</sub> = 0V to V+                                                     |                          |     | 50                       | Ω    |

| Switch Input Off Leakage                                         | I <sub>IN(OFF)</sub>    | V+ = 3.6V, V <sub>IN</sub> = 3.1V,<br>Unused inputs and V <sub>OUT</sub> = 0.5V         | -30                      |     | 30                       | nA   |

|                                                                  |                         | V+ = 3.6V, V <sub>IN</sub> = 0.5V,<br>Unused inputs and V <sub>OUT</sub> = 3.1V         | -30                      |     | <b>30</b>                | nA   |

| Switch Input Off Overvoltage Leakage                             | I <sub>IN(OFF-OV)</sub> | V+ = 3.6V, $V_{IN}$ = 7V,<br>Unused inputs and $V_{OUT}$ = 0V,<br>$T_A$ = +25°C, -55°C  | -30 30                   | 30  | nA                       |      |

|                                                                  |                         | T <sub>A</sub> = +125°C                                                                 | -30                      |     | 100                      | nA   |

|                                                                  |                         | Post radiation, +25°C                                                                   | -30                      |     | 100<br>30                |      |

| Switch On Input Leakage with<br>Overvoltage Applied to the Input | I <sub>IN(ON-OV)</sub>  | V+ = 3.6V, V <sub>IN</sub> = 7V, V <sub>OUT</sub> = OPEN                                | 1.8                      |     | 3.6                      | μA   |

| Switch Output Off Leakage                                        | I <sub>OUT(OFF)</sub>   | V+ = 3.6V, V <sub>OUT</sub> = 3.1V, All inputs = 0.5V,<br>T <sub>A</sub> = +25°C, -55°C | -30                      |     | 30                       | nA   |

|                                                                  |                         | T <sub>A</sub> = +125°C                                                                 | 0                        |     | 60                       | nA   |

|                                                                  |                         | Post radiation, +25°C                                                                   | -30                      |     | 30                       | nA   |

|                                                                  |                         | V+ = 3.6V, V <sub>OUT</sub> = 0.5V, All inputs = 3.1V,<br>T <sub>A</sub> = +25°C, -55°C | -30                      |     | 30                       | nA   |

|                                                                  |                         | T <sub>A</sub> = +125°C                                                                 | 0                        |     | 30                       | nA   |

|                                                                  |                         | Post radiation, +25°C                                                                   | -30                      |     | 30                       | nA   |

Recommended operating conditions, GND = 0V,  $V_{REF}$  = 3.3V,  $V_{IH}$  = 3.3V,  $V_{IL}$  = 0V,  $T_A$  = +25°C, unless otherwise noted. **Boldface limits** apply across the operating temperature range, -55°C to +125°C; over at total ionizing dose of 30 krad(Si) with exposure at a low dose rate of 43 MeV•cm²/mg. (Continued)

| Parameter                                    | Symbol               | Test Conditions                                                                                           | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|----------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| Switch Output Leakage with Switch<br>Enabled | I <sub>OUT(ON)</sub> | V+ = 3.6V, $V_{IN} = V_{OUT} = 3.1V$<br>All unused inputs at 0.5V,<br>$T_A = +25^{\circ}\text{C}$ , -55°C | -30                      |     | 30                       | nA   |

|                                              |                      | T <sub>A</sub> = +125°C                                                                                   | 0                        |     | 30                       | nA   |

|                                              |                      | Post radiation, +25°C                                                                                     | -30                      |     | 30                       | nA   |

|                                              |                      | V+ = 3.6V, $V_{IN} = V_{OUT} = 0.5V$<br>All unused inputs at 3.1V,<br>$T_A = +25^{\circ}\text{C}$ , -55°C | -30                      |     | 30                       | nA   |

|                                              |                      | T <sub>A</sub> = +125°C                                                                                   | 0                        |     | 30                       | nA   |

|                                              |                      | Post radiation, +25°C                                                                                     | -30                      |     | 30                       | nA   |

| Quiescent Supply Current                     | I <sub>SUPPLY</sub>  | V+ = V <sub>REF</sub> = V <sub>EN</sub> = 3.6V<br>V <sub>A</sub> = 0V, T <sub>A</sub> = +25°C, -55°C      |                          | 100 | nA                       |      |

|                                              |                      | T <sub>A</sub> = +125°C                                                                                   |                          |     | 300                      | nA   |

|                                              |                      | Post radiation, +25°C                                                                                     |                          |     | 300                      | nA   |

| Reference Quiescent Supply Current           | I <sub>REF</sub>     | V+ = V <sub>REF</sub> = V <sub>EN</sub> = 3.6V, V <sub>A</sub> = 0V                                       |                          |     | 200                      | nA   |

| Dynamic                                      |                      |                                                                                                           |                          |     |                          |      |

| Addressing Transition Time                   | t <sub>AHL</sub>     | V+ = 3V; <u>Figure 3</u>                                                                                  | 10                       |     | 100                      | ns   |

| Break-Before-Make Delay                      | t <sub>BBM</sub>     | V+ = 3V; <u>Figure 7</u>                                                                                  | 5                        | 25  | 50                       | ns   |

| Enable Turn-On Time                          | t <sub>EN(ON)</sub>  | V+ = 3V; <u>Figure 5</u>                                                                                  |                          |     | 50                       | ns   |

| Enable Turn-Off Time                         | t <sub>EN(OFF)</sub> | V+ = 3V; <u>Figure 5</u>                                                                                  |                          |     | 50                       | ns   |

#### Note:

<sup>7.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

## 3.6 Truth Table

| А3 | A2 | A1 | Α0 | EN | "ON" Channel |

|----|----|----|----|----|--------------|

| Х  | Х  | Х  | Х  | 1  | None         |

| 0  | 0  | 0  | 0  | 0  | 1            |

| 0  | 0  | 0  | 1  | 0  | 2            |

| 0  | 0  | 1  | 0  | 0  | 3            |

| 0  | 0  | 1  | 1  | 0  | 4            |

| 0  | 1  | 0  | 0  | 0  | 5            |

| 0  | 1  | 0  | 1  | 0  | 6            |

| 0  | 1  | 1  | 0  | 0  | 7            |

| 0  | 1  | 1  | 1  | 0  | 8            |

| 1  | 0  | 0  | 0  | 0  | 9            |

| 1  | 0  | 0  | 1  | 0  | 10           |

| 1  | 0  | 1  | 0  | 0  | 11           |

| 1  | 0  | 1  | 1  | 0  | 12           |

| 1  | 1  | 0  | 0  | 0  | 13           |

| 1  | 1  | 0  | 1  | 0  | 14           |

| 1  | 1  | 1  | 0  | 0  | 15           |

| 1  | 1  | 1  | 1  | 0  | 16           |

Note: X = Don't care, 1 = Logic High, 0 = Logic Low.

# 3.7 Timing Diagrams

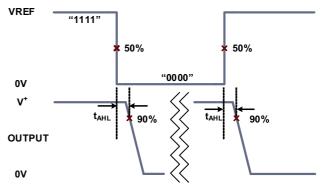

Figure 3. Address Time to Output Test Circuit

Figure 4. Address Time to Output Diagram

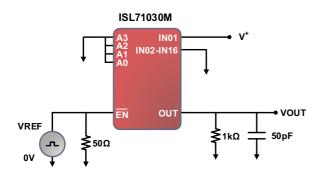

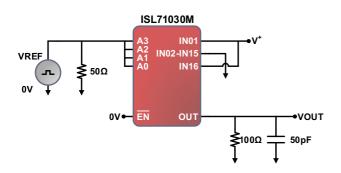

Figure 5. Time to Enable/Disable Output Test Circuit

Figure 6. Time to Enable/Disable Output Diagram

Figure 7. Break-Before-Make Test Circuit

Figure 8. Break-Before-Make Diagram

Figure 9. Charge Injection Test Circuit

Figure 10. Charge Injection Diagram

# **Typical Performance Graphs**

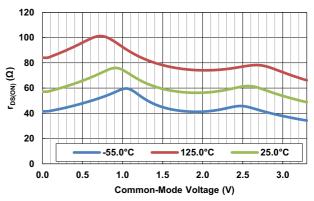

Figure 11.  $r_{DS(ON)}$  vs Common-Mode Voltage (V+ = 3V)

Figure 12.  $r_{DS(ON)}$  vs Common-Mode Voltage (V+ = 4.5V)

80

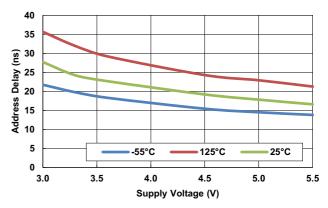

70 60 Address Delay (ns) 50 40 30 20 10 25°C -55°C 125°C 3.0 4.5 5.5 Supply Voltage (V)

Figure 13. Address Propagation Delay (High to Low)

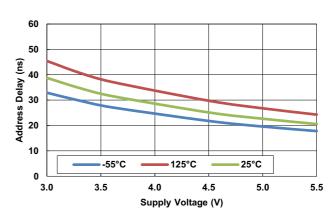

Figure 14. Address Propagation Delay (Low to High)

Figure 15. Address Propagation Delay

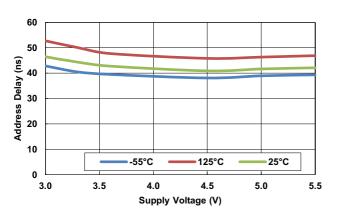

Figure 16. Break-Before-Make Delay

V+ = 5V,  $V_{REF}$  = 3.3V,  $V_{IN}$  = 0V,  $R_L$  = Open,  $T_A$  = +25°C, unless otherwise specified (Continued)

Figure 17. Break-Before-Make Delay

Figure 18. Enable to Output Propagation Delay

Figure 19. Disable to Output Propagation Delay

Figure 20. Enable/Disable Propagation Delay

Figure 21. Off Isolation (V+ = 5V, +25°C,  $R_L$  = 511 $\Omega$ )

Figure 22. Off Isolation (V+ = 5V, +25°C, R<sub>L</sub>= Open)

V+ = 5V,  $V_{REF}$  = 3.3V,  $V_{IN}$  = 0V,  $R_L$  = Open,  $T_A$  = +25°C, unless otherwise specified (Continued)

Figure 24. Charge Injection

# 5. Application Information

## 5.1 Power-Up Considerations

The circuit is insensitive to any given power-up sequence between V+ and VREF; however, Renesas recommends that all supplies power up relatively close to each other.

## 5.2 Overvoltage Protection

The ISL71030M has overvoltage protection on both the input and the output. On the output, the voltage is limited to a diode past the rails. Each of the inputs has independent overvoltage protection that works regardless of the switch being selected. If a switch experiences an overvoltage condition, the switch is turned off. As soon as the voltage returns within the rails, the switch returns to normal operation.

## 5.3 VREF and Logic Functionality

The VREF pin sets the logic threshold for the ISL71030M. The range for VREF is between 3V and 5.5V. The switching point is set to around 50% of the voltage presented to VREF. This switching point allows for both 5V and 3.3V logic control.

## 5.4 Considerations for Redundant Applications

When using the ISL71030M in a cold sparing application, Renesas recommends keeping the ground pin connected to system ground at all times. Both supply pins (V+ and VREF) should either be grounded or floating together.

If the supply pins are floating, Renesas recommends placing a high value bleed resistor ( $\sim 1 M\Omega$ ) in parallel with the decoupling capacitors on each supply pin to ensure that the supply voltage is discharged in a predictable manner. Figures 25 and 26 illustrate the recommended cold sparing setup for both shorted and floating supplies.

Figure 25. Cold Sparing Setup with Supplies Shorted

Figure 26. Cold Sparing Setup with Supplies Floating

#### 6. Radiation Tolerance

The ISL71030M is a radiation tolerant device for commercial space applications, Low Earth Orbit (LEO) applications, high altitude avionics, launch vehicles, and other harsh environments. This device's response to Total Ionizing Dose (TID) radiation effects and Single-Event Effects (SEE) has been measured, characterized, and reported in the following sections. However, TID performance is not guaranteed through radiation acceptance testing, nor is the SEE characterized performance guaranteed.

#### 6.1 Total Ionizing Dose (TID) Testing

#### 6.1.1 Introduction

This test was conducted to determine the sensitivity of the part to the total dose environment. Test downpoints were 0krad(Si), 10krad(Si), 20krad(Si), and 30krad(Si). The irradiations were followed by a biased anneal for 168 hours at +100°C. Total dose testing was performed using a Hopewell Designs N40 paronormic 60Co irradiator. The irradiations were performed at 0.00875rad(Si)/s. A PbAl box was used to shield the test fixture and devices under test against low energy secondary gamma radiation. The characterization matrix consisted of 24 samples irradiated under bias and 12 samples irradiated with all pins grounded.

Four control units were used to ensure repeatable data. Two different wafers were used.

#### 6.1.2 Results

Table 1 summarizes the attributes data. "Bin 1" indicates a device that passes all datasheet specification limits.

Table 1. Total Dose Test Attributes Data

| Dose Rate | Bias     | Sample Size | Downpoint  | Bin 1 | Rejects |

|-----------|----------|-------------|------------|-------|---------|

| 8.75      | Biased   | 16          | Pre-rad    | 16    | 0       |

|           |          |             | 10krad(Si) | 16    | 0       |

|           |          |             | 20krad(Si) | 16    | 0       |

|           |          |             | 30krad(Si) | 16    | 0       |

|           |          |             | Anneal     | 16    | 0       |

| 8.75      | Grounded | 16          | Pre-rad    | 16    | 0       |

|           |          |             | 10krad(Si) | 16    | 0       |

|           |          | 20krad(Si)  | 16         | 0     |         |

|           |          | 8           | 30krad(Si) | 16    | 0       |

|           |          |             | Anneal     | 16    | 0       |

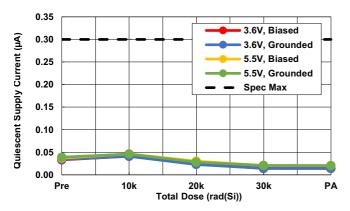

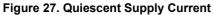

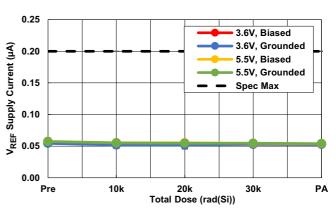

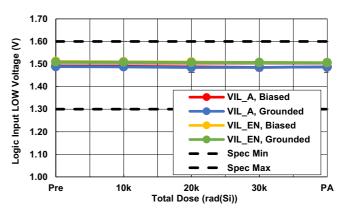

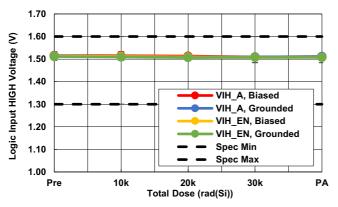

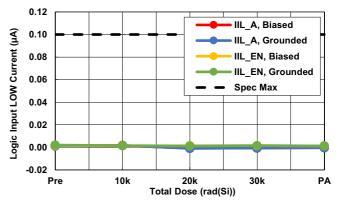

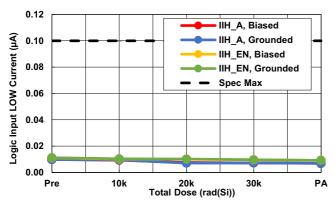

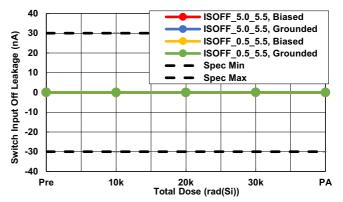

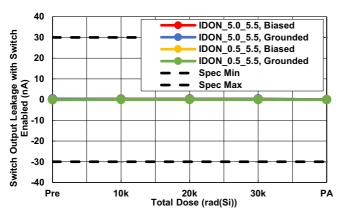

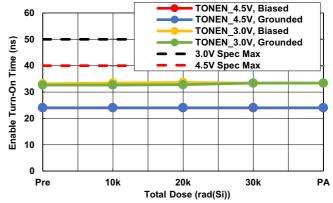

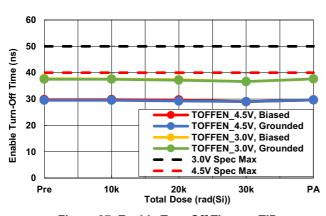

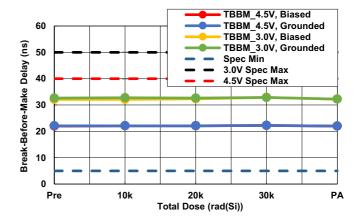

<u>Figures 27</u> through <u>38</u> show data for key parameters at all downpoints. The plots show the average as a function of total dose for each of the irradiation conditions; we chose to use the average because of the relatively large sample sizes. All parts showed excellent stability over radiation.

# 6.1.3 Typical Radiation Performance Graphs

Figure 28. VREF Supply Current vs TID

Figure 29. Switch ON Resistance vs TID

Figure 30. Logic Input LOW Voltage vs TID

Figure 31. Logic Input HIGH Voltage vs TID

Figure 32. Logic Input LOW Current vs TID

Figure 33. Logic Input HIGH Current vs TID

Figure 34. Switch Input Off Leakage vs TID

Figure 35. Output Leakage with Switch Enabled vs TID

Figure 36. Enable Turn-On Time vs TID

Figure 37. Enable Turn-Off Time vs TID

Figure 38. Break-Before-Make Delay vs TID

#### 6.1.4 Conclusion

The ISL71030M 16-channel analog multiplexer was tested at low dose rate under biased and unbiased conditions to 30krad(Si) as outlined in MIL-STD-883 Test Method 1019.7. The samples were also taken through a high temperature biased anneal at 100C for 168 hours. ATE characterization testing at each down-point showed no rejects to the datasheet limits after irradiation or after the high temperature anneal. All parameters showed excellent stability.

Table 2. ISL71030M Response of Key Parameters vs TID

| Parameter                        | Condition | Bias              | Pre-Rad<br>Value | 10krad(Si) | 20krad(Si) | 30krad(Si) | Post<br>Anneal | Units |

|----------------------------------|-----------|-------------------|------------------|------------|------------|------------|----------------|-------|

| Switch ON-Resistance             | Min       | Avg (Biased)      | 48.99            | 48.98      | 48.87      | 48.84      | 48.80          | Ω     |

|                                  |           | Avg<br>(Unbiased) | 48.60            | 48.62      | 48.61      | 48.84      | 48.80          | Ω     |

|                                  | Max       | Avg (Biased)      | 68.36            | 68.26      | 68.18      | 67.95      | 67.89          | Ω     |

|                                  |           | Avg<br>(Unbiased) | 68.01            | 67.91      | 67.83      | 67.95      | 67.89          | Ω     |

|                                  |           | Limit -           | -                | -          | -          | -          | ı              | Ω     |

|                                  |           | Limit +           | 120              | 120        | 120        | 120        | 120            | Ω     |

| Switch ON-Resistance Match       |           | Avg (Biased)      | 1.01             | 1.06       | 1.14       | 1.08       | 1.00           | Ω     |

| Between Channels                 |           | Avg<br>(Unbiased) | 1.02             | 1.04       | 1.04       | 1.08       | 1.00           | Ω     |

|                                  |           | Limit -           | -                | -          | -          | -          | ı              | Ω     |

|                                  |           | Limit +           | 5                | 5          | 5          | 5          | 5              | Ω     |

| Switch ON-Resistance Flatness    |           | Avg (Biased)      | 19.38            | 19.28      | 19.31      | 19.10      | 19.10          | Ω     |

|                                  |           | Avg<br>(Unbiased) | 19.41            | 19.29      | 19.22      | 19.10      | 19.10          | Ω     |

|                                  |           | Limit -           | -                | -          | -          | -          | ı              | Ω     |

|                                  |           | Limit +           | 40               | 40         | 40         | 40         | 40             | Ω     |

| Switch Input Off Leakage         |           | Avg (Biased)      | -0.004           | -0.111     | -0.039     | 0.006      | -0.057         | nA    |

|                                  |           | Avg<br>(Unbiased) | -0.002           | -0.098     | -0.044     | 0.006      | -0.057         | nA    |

|                                  |           | Limit -           | -30              | -30        | -30        | -30        | -30            | nA    |

|                                  |           | Limit +           | 30               | 30         | 30         | 30         | 30             | nA    |

| Switch Input Off Overvoltage     |           | Avg (Biased)      | 0.00             | -0.11      | -0.04      | 0.01       | -0.06          | nA    |

| Leakage                          |           | Avg<br>(Unbiased) | 0.00             | -0.10      | -0.04      | 0.01       | -0.06          | nA    |

|                                  |           | Limit -           | -30              | -30        | -30        | -30        | -30            | nA    |

|                                  |           | Limit +           | 30               | 30         | 30         | 30         | 30             | nA    |

| Switch Input Off Leakage with    |           | Avg (Biased)      | 0.08             | 0.10       | 0.10       | 0.22       | 0.16           | nA    |

| Supply Voltage Grounded          |           | Avg<br>(Unbiased) | 0.07             | 0.12       | 0.20       | 0.22       | 0.16           | nA    |

|                                  |           | Limit -           | -20              | -20        | -20        | -20        | -20            | nA    |

|                                  |           | Limit +           | 20               | 20         | 20         | 20         | 20             | nA    |

| Switch Input Off Leakage with    |           | Avg (Biased)      | 0.27             | 0.17       | 0.30       | 0.25       | 0.42           | nA    |

| Supply Voltage Open              |           | Avg<br>(Unbiased) | 0.27             | 0.35       | 0.44       | 0.25       | 0.42           | nA    |

|                                  |           | Limit -           | -20              | -20        | -20        | -20        | -20            | nA    |

|                                  |           | Limit +           | 20               | 20         | 20         | 20         | 20             | nA    |

| Switch On Input Leakage with     |           | Avg (Biased)      | 4.12             | 4.12       | 4.11       | 4.10       | 4.10           | μΑ    |

| Overvoltage Applied to the Input |           | Avg<br>(Unbiased) | 4.11             | 4.12       | 4.11       | 4.10       | 4.10           | μA    |

|                                  |           | Limit -           | 2.75             | 2.75       | 2.75       | 2.75       | 2.75           | μA    |

|                                  |           | Limit +           | 5.50             | 5.50       | 5.50       | 5.50       | 5.50           | μΑ    |

Table 2. ISL71030M Response of Key Parameters vs TID (Continued)

| Parameter                         | Condition | Bias              | Pre-Rad<br>Value | 10krad(Si) | 20krad(Si) | 30krad(Si) | Post<br>Anneal | Units |

|-----------------------------------|-----------|-------------------|------------------|------------|------------|------------|----------------|-------|

| Switch Output OFF Leakage         |           | Avg (Biased)      | 0.08             | 0.03       | 0.16       | 0.07       | 0.06           | nA    |

|                                   |           | Avg<br>(Unbiased) | 0.07             | 0.03       | 0.16       | 0.07       | 0.06           | nA    |

|                                   |           | Limit -           | -30              | -30        | -30        | -30        | -30            | nA    |

|                                   |           | Limit +           | 30               | 30         | 30         | 30         | 30             | nA    |

| Switch Output Leakage with Switch |           | Avg (Biased)      | 0.32             | 0.28       | 0.33       | 0.31       | 0.28           | nA    |

| Enabled                           |           | Avg<br>(Unbiased) | 0.32             | 0.29       | 0.32       | 0.31       | 0.28           | nA    |

|                                   |           | Limit -           | -30              | -30        | -30        | -30        | -30            | nA    |

|                                   |           | Limit +           | 30               | 30         | 30         | 30         | 30             | nA    |

| Logic Input LOW Voltage           |           | Avg (Biased)      | 1.49             | 1.49       | 1.49       | 1.49       | 1.49           | V     |

|                                   |           | Avg<br>(Unbiased) | 1.49             | 1.49       | 1.48       | 1.49       | 1.49           | V     |

|                                   |           | Limit -           | 1.3              | 1.3        | 1.3        | 1.3        | 1.3            | V     |

|                                   |           | Limit +           | 1.6              | 1.6        | 1.6        | 1.6        | 1.6            | V     |

| Logic Input HIGH Voltage          |           | Avg (Biased)      | 1.52             | 1.51       | 1.51       | 1.51       | 1.51           | V     |

|                                   |           | Avg<br>(Unbiased) | 1.51             | 1.51       | 1.51       | 1.51       | 1.51           | V     |

|                                   |           | Limit -           | 1.3              | 1.3        | 1.3        | 1.3        | 1.3            | V     |

|                                   |           | Limit +           | 1.6              | 1.6        | 1.6        | 1.6        | 1.6            | V     |

| Logic Input LOW Current           | ADDR      | Avg (Biased)      | 0.0012           | 0.0017     | -0.0008    | -0.0006    | -0.0003        | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.0010           | 0.0016     | -0.0009    | -0.0006    | -0.0003        | μΑ    |

|                                   | EN        | Avg (Biased)      | 0.0017           | 0.0015     | 0.0014     | 0.0015     | 0.0013         | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.0020           | 0.0015     | 0.0012     | 0.0015     | 0.0013         | μА    |

|                                   |           | Limit -           | -                | -          | -          | -          | -              | μΑ    |

|                                   |           | Limit +           | 0.10             | 0.10       | 0.10       | 0.10       | 0.10           | μΑ    |

| Logic Input HIGH Current          | ADDR      | Avg (Biased)      | 0.01             | 0.01       | 0.01       | 0.01       | 0.01           | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.01             | 0.01       | 0.01       | 0.01       | 0.01           | μА    |

|                                   | EN        | Avg (Biased)      | 0.01             | 0.01       | 0.01       | 0.01       | 0.01           | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.01             | 0.01       | 0.01       | 0.01       | 0.01           | μΑ    |

|                                   |           | Limit -           | -                | -          | -          | -          | -              | μΑ    |

|                                   |           | Limit +           | 0.10             | 0.10       | 0.10       | 0.10       | 0.10           | μΑ    |

| Quiescent Supply Current          | 3.6V      | Avg (Biased)      | 0.033            | 0.041      | 0.024      | 0.014      | 0.014          | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.034            | 0.041      | 0.023      | 0.014      | 0.014          | μΑ    |

|                                   | 5.5V      | Avg (Biased)      | 0.037            | 0.046      | 0.030      | 0.021      | 0.021          | μΑ    |

|                                   |           | Avg<br>(Unbiased) | 0.039            | 0.046      | 0.028      | 0.021      | 0.021          | μΑ    |

|                                   |           | Limit -           | -                | -          | -          | -          | -              | μΑ    |

|                                   |           | Limit +           | 0.3              | 0.3        | 0.3        | 0.3        | 0.3            | μΑ    |

Table 2. ISL71030M Response of Key Parameters vs TID (Continued)

| Parameter                  | Condition | Bias              | Pre-Rad<br>Value | 10krad(Si) | 20krad(Si) | 30krad(Si) | Post<br>Anneal | Units |

|----------------------------|-----------|-------------------|------------------|------------|------------|------------|----------------|-------|

| VREF Supply Current        | 3.6V      | Avg (Biased)      | 0.055            | 0.052      | 0.052      | 0.053      | 0.053          | μΑ    |

|                            |           | Avg<br>(Unbiased) | 0.054            | 0.052      | 0.052      | 0.053      | 0.053          | μА    |

|                            | 5.5V      | Avg (Biased)      | 0.058            | 0.055      | 0.055      | 0.055      | 0.054          | μΑ    |

|                            |           | Avg<br>(Unbiased) | 0.057            | 0.055      | 0.055      | 0.055      | 0.054          | μА    |

|                            |           | Limit -           | -                | -          | -          | -          | ı              | μΑ    |

|                            |           | Limit +           | 0.2              | 0.2        | 0.2        | 0.2        | 0.2            | μΑ    |

| Addressing Transition Time | 3.0V      | Avg (Biased)      | 38.13            | 38.13      | 38.13      | 38.25      | 38.13          | ns    |

|                            |           | Avg<br>(Unbiased) | 38.00            | 38.00      | 38.00      | 38.25      | 38.13          | ns    |

|                            | 4.5V      | Avg (Biased)      | 59.88            | 59.88      | 59.88      | 59.75      | 59.88          | ns    |

|                            |           | Avg<br>(Unbiased) | 59.63            | 59.75      | 59.75      | 59.75      | 59.88          | ns    |

|                            |           | Limit -           | 10               | 10         | 10         | 10         | 10             | ns    |

|                            |           | 3.0V Limit +      | 100              | 100        | 100        | 100        | 100            | ns    |

|                            |           | 4.5V Limit +      | 70               | 70         | 70         | 70         | 70             | ns    |

| Break-Before-Make Delay    | 3.0V      | Avg (Biased)      | 32.13            | 32.13      | 32.38      | 32.88      | 32.25          | ns    |

|                            |           | Avg<br>(Unbiased) | 32.63            | 32.75      | 32.63      | 32.88      | 32.25          | ns    |

|                            | 4.5V      | Avg (Biased)      | 22.00            | 22.13      | 22.13      | 22.25      | 22.00          | ns    |

|                            |           | Avg<br>(Unbiased) | 22.13            | 22.13      | 22.13      | 22.25      | 22.00          | ns    |

|                            |           | Limit -           | 5                | 5          | 5          | 5          | 5              | ns    |

|                            |           | 3.0V Limit +      | 50               | 50         | 50         | 50         | 50             | ns    |

|                            |           | 4.5V Limit +      | 40               | 40         | 40         | 40         | 40             | ns    |

| Enable Turn-On Time        | 3.0V      | Avg (Biased)      | 33.13            | 33.38      | 33.63      | 33.38      | 33.38          | ns    |

|                            |           | Avg<br>(Unbiased) | 32.63            | 32.63      | 32.75      | 33.38      | 33.38          | ns    |

|                            | 4.5V      | Avg (Biased)      | 24.00            | 24.00      | 24.00      | 24.00      | 24.00          | ns    |

|                            |           | Avg<br>(Unbiased) | 24.00            | 24.00      | 24.00      | 24.00      | 24.00          | ns    |

|                            |           | Limit -           | -                | -          | -          | -          | ı              | ns    |

|                            |           | 3.0V Limit +      | 50               | 50         | 50         | 50         | 50             | ns    |

|                            |           | 4.5V Limit +      | 40               | 40         | 40         | 40         | 40             | ns    |

| Enable Turn-Off Time       | 3.0V      | Avg (Biased)      | 37.75            | 37.63      | 37.38      | 36.63      | 37.63          | ns    |

|                            |           | Avg<br>(Unbiased) | 37.50            | 37.50      | 37.13      | 36.63      | 37.63          | ns    |

|                            | 4.5V      | Avg (Biased)      | 29.75            | 29.75      | 29.63      | 29.00      | 29.63          | ns    |

|                            |           | Avg<br>(Unbiased) | 29.50            | 29.50      | 29.25      | 29.00      | 29.63          | ns    |

|                            |           | Limit -           | -                | -          | -          | -          | 1              | ns    |

|                            |           | 3.0V Limit +      | 50               | 50         | 50         | 50         | 50             | ns    |

|                            |           | 4.5V Limit +      | 40               | 40         | 40         | 40         | 40             | ns    |

# 6.2 Single-Event Effects Testing

The intense heavy ion environment encountered in space applications can cause a variety of Single-Event Effects (SEE). SEE can lead to system-level performance issues including disruption, degradation, and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response. The following is a summary of the ISL71030M SEE testing.

## 6.2.1 SEE Test Facility

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility on April 3, 2019. The overall test setup includes the test jig containing four evaluation boards mounted and wired through a 20ft cable to the data room. The end of the 20ft cable in the data room was connected to a switchboard. The switchboard was wired to the power supplies and monitoring equipment/scopes.

#### 6.2.2 SEE Test Setups

Testing the ISL71030M parts for damaging SEE (Single Event Burnout (SEB) and Single Event Latch-Up (SEL)) had the parts configured to select input 13 by applying the test voltage, VTEST, to address lines A2 and A3 and GND to A0, A1, and EN-bar. This connected IN-13 to the output. The output was loaded with a  $10k\Omega$  resistor to GND, and the input (IN-13) had a  $10k\Omega$  resistor to the test voltage, VTEST. This created a resistor divider that put the output, OUT, at half of VTEST. The test voltage, VTEST, was also applied to the supply, V+, and to the inputs 9 to 16, excluding 13. The inputs 1 to 8 had GND applied to them. The parts tested for damaging SEE were heated with a thin-film heater on the back of the PCB to attain a case temperature of  $125^{\circ}$ C.

Single Event Transients (SET) were tested with VTEST at 3.00V and 5.50V, the extremes of the suggested operating range. For SET the parts were not heated and therefore were at the ambient of about 25°C. The definition of a SET was a  $\pm 20$ mV movement of OUT from its nominal value of half VTEST. As with the SEB testing, the part was configured to select input 13. However, unlike the SEB testing, the addressing was done with applied voltages of 70% VREF on A2 and A3, and 30% VREF applied to A0, A1, and EN-bar. This was done to place the addressing at low noise margin states as VREF was set to 3.00V. OUT had a 10k $\Omega$  resistor to GND and IN 13 was supplied with VTEST through a 10k $\Omega$  resistor to again set OUT to half of VTEST.

#### 6.2.3 Single Event Burnout and Latch-Up (SEB/L) Results

The test voltage, VTEST, was sequentially set to 6.50V, 6.75V, and 7.00V for three independent irradiations on four parts. Before and after each irradiation the total current to V+ and VREF was measured along with the output voltage, OUT. No deviations greater than 3% were registered for the currents, and no deviation of even 1% was seen on OUT. The conclusion was that no permanent damage resulted from the irradiations as done.

#### 6.2.4 SET Results

No SET were captured with the  $\pm 20$ mV criterion in the most recent testing. This result is inconsistent with previous testing on a similar part. In the earlier testing, the  $\pm 20$ mV SET corresponded to cross sections of  $419\mu\text{m}^2$  at VTEST = 3.0V and  $2020\mu\text{m}^2$  at VTEST = 5.5V. However, the nature of the SET captures was that a spike transient triggered the capture at  $\pm 20$ mV but the low frequency motion on the OUT node without the spike was less than  $\pm 20$ mV. Examples are presented below from the previous testing. Thus, the captures previously were dependent on the high-frequency coupling. A slight change in this could have dropped the SET below the trigger point for the newer testing. Because there are no SET to examine for the newer testing, this is all supposition. However, the older testing still represents a worst case estimate of the ISL71030M SET behavior. The previous testing did provide evidence that the  $\pm 20$ mV SET vanished at an LET of 20MeV·cm²/mg. This should also apply to the ISL71030M.

Figure 39. Composite Plot of 20 Largest and Longest SET for Both Positive and Negative Deviations Seen on Previous Testing, DUT 1-4 at LET = 43MeV·cm<sup>2</sup>/mg and V+ = 5.5V.

#### 6.2.5 Conclusion

The ISL71030M 5V MUX is immune to damaging SEE when operated at 125°C and V+ voltages up to 7V while being irradiated with normal incidence silver for a surface LET of  $43\text{MeV}\cdot\text{cm}^2/\text{mg}$ . The maximum cross section for damaging events under these conditions is  $2.5\mu\text{m}^2$  (zero events on four units to  $1\times10^7$ ions/cm<sup>2</sup>).

SET on the ISL71030M for  $\pm 20$ mV on OUT fall somewhere between  $2020\mu m^2$  and zero depending on the testing cited. Those SET that were captured were marginal to the  $\pm 20$ mV criterion. The  $\pm 20$ mV SET disappeared completely at 20MeV·cm²/mg.

ISL71030M 7. Revision History

# 7. Revision History

| Rev. | Date         | Description                                                                                                  |

|------|--------------|--------------------------------------------------------------------------------------------------------------|

| 1.01 | Apr 12, 2021 | Added two features bullets:  Passes NASA low outgassing specifications NiPdAu lead finish (Pb-free, Sn-free) |

| 1.00 | Jul 10, 2019 | Initial Release                                                                                              |

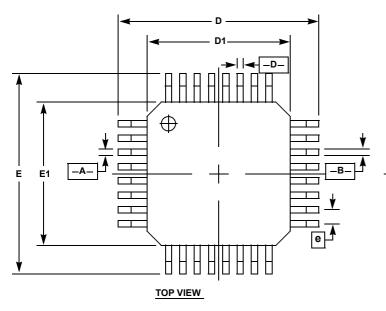

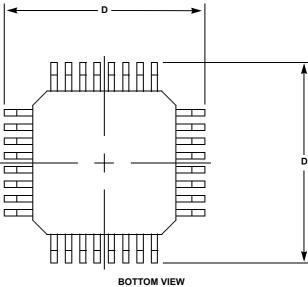

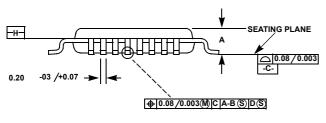

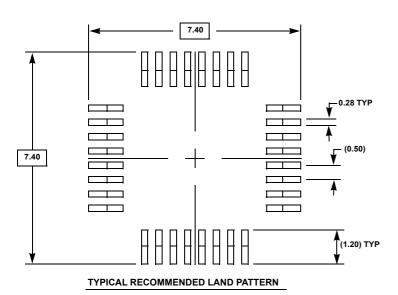

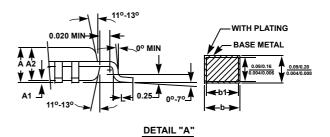

# 8. Package Outline Drawing

For the most recent package outline drawing, see Q32.5x5A.

Q32.5X5A 32 Lead Thin Plastic Quad Flatpack Package (TQFP) Rev 1, 10/11

SIDE VIEW

| SCALE NONE |                 |       |   |  |  |  |  |  |

|------------|-----------------|-------|---|--|--|--|--|--|

| SYMBOL     | L MIN MAX NOTES |       |   |  |  |  |  |  |

| Α          | -               | 1.13  | - |  |  |  |  |  |

| A1         | 0.039           | 0.089 | - |  |  |  |  |  |

| A2         | 0.95            | 1.05  | - |  |  |  |  |  |

| b          | 0.17            | 6     |   |  |  |  |  |  |

| b1         | 0.17            | -     |   |  |  |  |  |  |

| D          | 7 B             | -     |   |  |  |  |  |  |

| Е          | 7 B             | 7 BSC |   |  |  |  |  |  |

| D1         | 5 B             | -     |   |  |  |  |  |  |

| E1         | 5 BSC -         |       |   |  |  |  |  |  |

| е          | 0.5             | -     |   |  |  |  |  |  |

| L          | 0.45            | -     |   |  |  |  |  |  |

| N          | 3               | 6     |   |  |  |  |  |  |

#### NOTES:

- 1. Controlling Dimension; Millimeter, converted inch dimensions are not necessarily exact.

- 2. All dimensioning and tolerancing conform to ANSI Y14.5-1982.

- 3. Dimensions D and E to be determined at seating plane -C-  $\,$

- 4. Dimensions D1 and E1 to be determined at datum plane -H-

- Dimensions D1 and E1 do not include mold protusion. Allowable protusion is 0.25mm (0.010 inch) per side.

- 6. Dimension b does not include dambar protusion. Allowable dambar protusion shall not cause the lead width to exceed the maximum b dimensions by more than 0.08mm (0.0003 inch).

- 7. "N" is the number of terminal position.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/